- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄375864 > FMS7401 (Fairchild Semiconductor Corporation) Digital Power Controller PDF資料下載

參數(shù)資料

| 型號: | FMS7401 |

| 廠商: | Fairchild Semiconductor Corporation |

| 元件分類: | 基準(zhǔn)電壓源/電流源 |

| 英文描述: | Digital Power Controller |

| 中文描述: | 數(shù)字電源控制器 |

| 文件頁數(shù): | 41/80頁 |

| 文件大小: | 1535K |

| 代理商: | FMS7401 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁當(dāng)前第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁

PRODUCT SPECIFICATION

FMS7401/7401L

REV. 1.0.2 6/23/04

41

7

Timer 0 Circuit

Timer 0’s main circuit is a 12-bit free running up-counter whose clock source is the main system instruction clock (F

ICLK

). The

main counter may be used to generate microcontroller hardware interrupts and serve as a prescaler for the Idle and Watchdog

Timers.

After power-up or any system reset, the Timer 0’s 12-bit counter is initialized to 0x000 and continuously increments with each

instruction clock. The 12-bit counter is not memory mapped; therefore, software cannot read or write to the counter registers.

However, software may monitor the Timer 0’s main counter by reading the state of the Timer 0 Pending (T0PND) bit of the

Timer 0 Control (T0CNTRL) memory mapped register.

1

The T0PND flag is automatically set with each counter overflow

(a transition from 0xFFF to 0x000) which occurs after every 4,096 cycles. At every overflow, the counter rolls over to 0x000

and continues to increment. In order for software to properly monitor the main counter, the T0PND bit must be cleared before

the next counter overflow.

The T0CNTRL register houses two hardware interrupt enable bits. The WKINTEN register bit is the MIW hardware interrupt

enable bit. For details regarding its usage refer to the

Multi-input Wakeup Circuit

section of the datasheet. The T0INTEN

register bit is Timer 0’s microcontroller hardware interrupt (TMRI0) enable bit. If set, hardware interrupts are enabled and

trigger by the T0PND flag.

2

As long as a Timer 0 pending flag is set, the hardware interrupt will continue to execute software’s

Timer 0 interrupt service routine until the pending flag is cleared.

3

The SBIT or RBIT instructions may be used to either set or clear the T0INTEN or WKINTEN bits. The SBIT and RBIT

instructions both take two instruction clock cycles to complete their execution. In the first cycle, all register bits are automati-

cally read to obtain their most current value. In the second cycle, the bit to be set/cleared is given its new value and all bits are

then re-written to the register. Using the SBIT/RBIT instruction to set/clear an enable bit with a pending flag in the same regis-

ter may cause a potential hazard. Software may inadvertently clear a recently triggered pending flag if the trigger happened

during the second phase of the SBIT/RBIT instruction execution. To avoid this condition, the LD instruction must be used to

set or clear the interrupt enable bits. The Timer 0 circuit is designed such that software may not trigger a pending flag by writ-

ing a 1 to a T0PND register bit, it may only be cleared. The action of writing a 1 to a T0PND register bit holds the current bit

value. The action of writing a 0 to a T0PND register bit clears the bit value. Therefore, the “LD T0CNTRL, #083H” instruction

will set both interrupt enable bits without clearing T0PND.

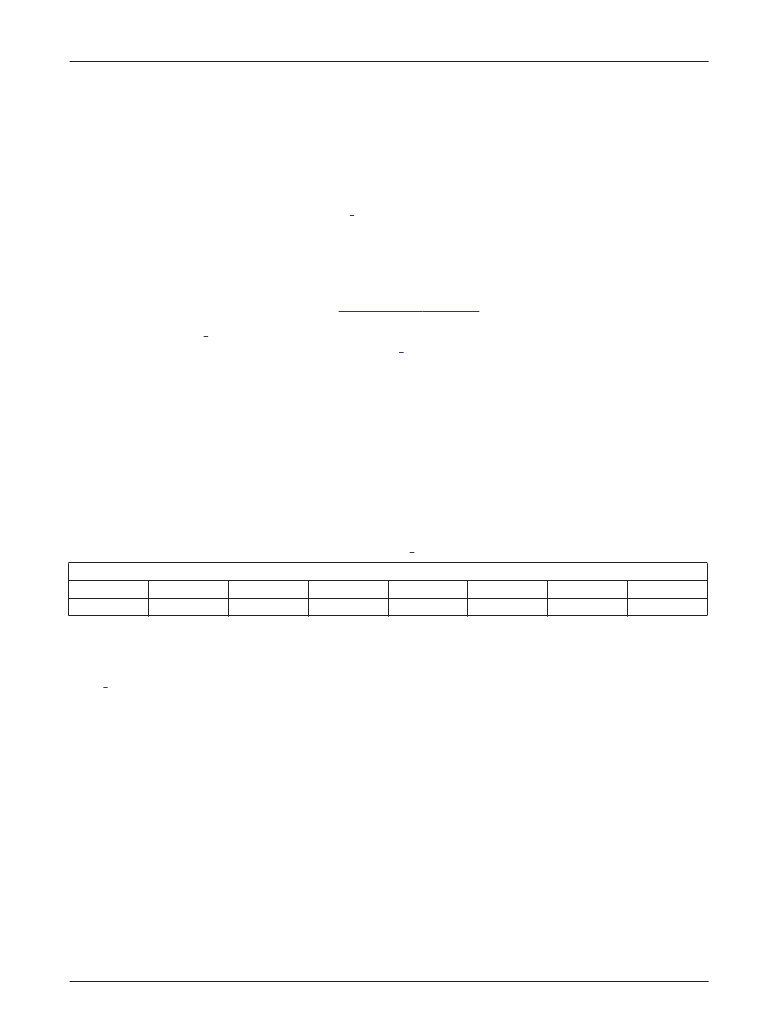

Table 18. Timer 0 Control (T0CNTRL) Register Definitions

4

7.1

Once the device enters Idle Mode, the microcontroller core and other main circuits are disabled for current conservation. The

Idle Timer will automatically wake the device from Idle Mode, if the MIW has not already done so, after a maximum of 8,192

cycles.

5

Idle Timer

The Idle Timer is a 1-bit extension of the Timer 0’s main 12-bit up-counter. With each overflow of the main counter, the Idle

Timer extension bit is toggled essentially causing the Idle Timer overflow to occur after 8,192 cycles. Once the Idle Timer

overflow flag is triggered, the device wakes from Idle Mode and starts its instruction execution with the next clock cycle.

The Idle Timer overflow flag cannot be monitored by software. Therefore, in order to maximize the time that the device

remains in Idle Mode software must monitor the T0PND flag. Once the T0PND flag is triggered, software may then issue the

Idle Mode command. Software may also loop on the Idle Mode command to extend the average time the device remains in Idle

Mode, thereby reducing the overall current consumption.

7.2

The Watchdog Timer is used to safely recover the device in the rare event of a processor “runaway condition” by issuing a sys-

tem reset. A Watchdog Timer runs continuously with Timer 0’s main 12-bit up-counter; however, a Watchdog Reset will not

Watchdog Timer

T0CNTRL Register (addr. 0xB6)

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

WKINTEN

x

x

x

x

x

T0PND

T0INTEN

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| FMS7401LEN | Digital Power Controller |

| FMS7401LEN14 | Digital Power Controller |

| FMS7401LVN | Digital Power Controller |

| FMS7401LVN14 | Digital Power Controller |

| FMS7G10US60S | SWTCH ROLLER SPDT 20A SCRW TERM |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| FMS7401L | 制造商:FAIRCHILD 制造商全稱:Fairchild Semiconductor 功能描述:Digital Power Controller |

| FMS7401L_05 | 制造商:FAIRCHILD 制造商全稱:Fairchild Semiconductor 功能描述:Digital Power Controller |

| FMS7401LA_ABA3026U WAF | 制造商:Fairchild Semiconductor Corporation 功能描述: |

| FMS7401LEM8X | 制造商:FAIRCHILD 制造商全稱:Fairchild Semiconductor 功能描述:Digital Power Controller |

| FMS7401LEMT8X | 制造商:FAIRCHILD 制造商全稱:Fairchild Semiconductor 功能描述:Digital Power Controller |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。