- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄360868 > IP101 PHY 10/100M Single Chip Fast Ethernet Transceiver PDF資料下載

參數(shù)資料

| 型號: | IP101 |

| 英文描述: | PHY 10/100M Single Chip Fast Ethernet Transceiver |

| 中文描述: | 單芯片物理層10/100M自適應(yīng)快速以太網(wǎng)收發(fā)器 |

| 文件頁數(shù): | 5/33頁 |

| 文件大?。?/td> | 821K |

| 代理商: | IP101 |

第1頁第2頁第3頁第4頁當(dāng)前第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁

IP101

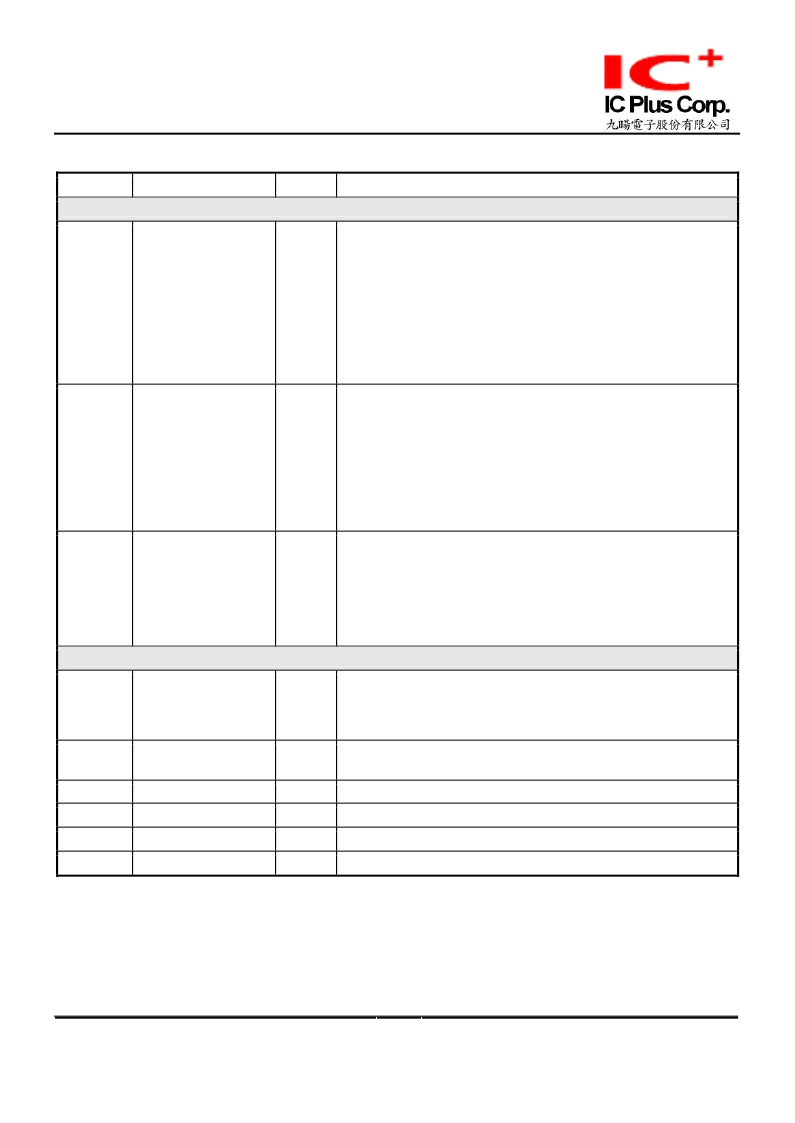

5.0 Pin Descriptions

(continued)

Pin no.

IP101-DS-R0.02

Feb. 24, 2003

5 / 33

Copyright

2003, IC Plus Corp.

Confidential, All rights reserved.

Advanced, Specification subject to change without notice.

NOT APPROVED BY TECHNICAL DOCUMENT CONTROL

Label

Type

Description

MII and PCS Interface – Media Independent Interface (MII) Pins

24

RX_ER/

FIBMOD

O/LI

(PD)

Receive error:

This pin outputs a high status when errors

occurred in the decoded data in the transmission.

Fiber Mode:

During power on reset, this pin status is latched to

determine at which media mode to operate:

1: Fiber mode

0: UTP mode

An internal weak pull low resistor sets this to the default of UTP

mode. It is possible to use an external 5.1K

pull high resistor to

enable fiber mode.

After power on, the pin operates as the Receive Error pin.

1

COL/RMII

O/LI

(PD)

Collision Detected:

When this pin outputs a high status signal it

means collision is detected.

RMII Mode:

During power on reset, this pin status is latched and

arranged with MII/SNIB (pin44) to determine MAC interface

RMII MII/SNIB

1 X RMII Interface

0 1 MII Interface

0 0 SNII Interface

(

Notice:

This pin is pulled down internally)

23

CRS/LEDMOD

O

(PD)

Carrier Sense:

When signal output from this pin is high indicates

the transmission is in process and at low status means the line is

in idle state.

LEDMOD:

During power on reset, this pin status is latched to

determine at which LED mode to operate, please refer to the LED

pins description.

(

Notice:

This pin is pulled down internally)

RMII (Reduced MII)

7

REF_CLK

I

Reference Clock:

This pin is an input pin operates as RMII

reference clock (REF_CLK) under RMII mode. 25MHz Crystal

Input and Output, X1 & X2, should be disconnected when

REF_CLK is used as the clock source of IP108.

2

TX_EN

I

(PD)

Transmit Enable:

For MAC to indicate transmit operation

5,6

TXD[1:0]

I

Transmit two-bit Data

24

RX_ER

I/O

Receive Error

22

CRS_DV

O

Carrier Sense and Receive Data Valid

20, 21

RXD[1:0]

O

Received two-bit Data

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| IP1060AD | Analog IC |

| IP1060AJ | Voltage-Mode SMPS Controller |

| IP1060AN | Analog IC |

| IP1060BJ | Voltage-Mode SMPS Controller |

| IP1060D | Analog IC |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| IP101ALF | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Single port 10/100 Fast Ethernet Transceiver |

| IP101ALF-DS-R01 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Single port 10/100 Fast Ethernet Transceiver |

| IP101ALF-DS-R02 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Single port 10/100 Fast Ethernet Transceiver |

| IP101ALF-DS-R03 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Single port 10/100 Fast Ethernet Transceiver |

| IP101ALF-DS-R04 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Single port 10/100 Fast Ethernet Transceiver |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。