- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄67723 > ISP1583ET1,118 (ST-ERICSSON) UNIVERSAL SERIAL BUS CONTROLLER, PBGA64 PDF資料下載

參數(shù)資料

| 型號: | ISP1583ET1,118 |

| 廠商: | ST-ERICSSON |

| 元件分類: | 總線控制器 |

| 英文描述: | UNIVERSAL SERIAL BUS CONTROLLER, PBGA64 |

| 封裝: | 4 X 4 MM, 0.80 MM HEIGHT, LEAD FREE, PLASTIC, SOT969-1,TFBGA-64 |

| 文件頁數(shù): | 15/100頁 |

| 文件大小: | 508K |

| 代理商: | ISP1583ET1,118 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁當(dāng)前第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁

ISP1583_7

NXP B.V. 2008. All rights reserved.

Product data sheet

Rev. 07 — 22 September 2008

20 of 99

NXP Semiconductors

ISP1583

Hi-Speed USB peripheral controller

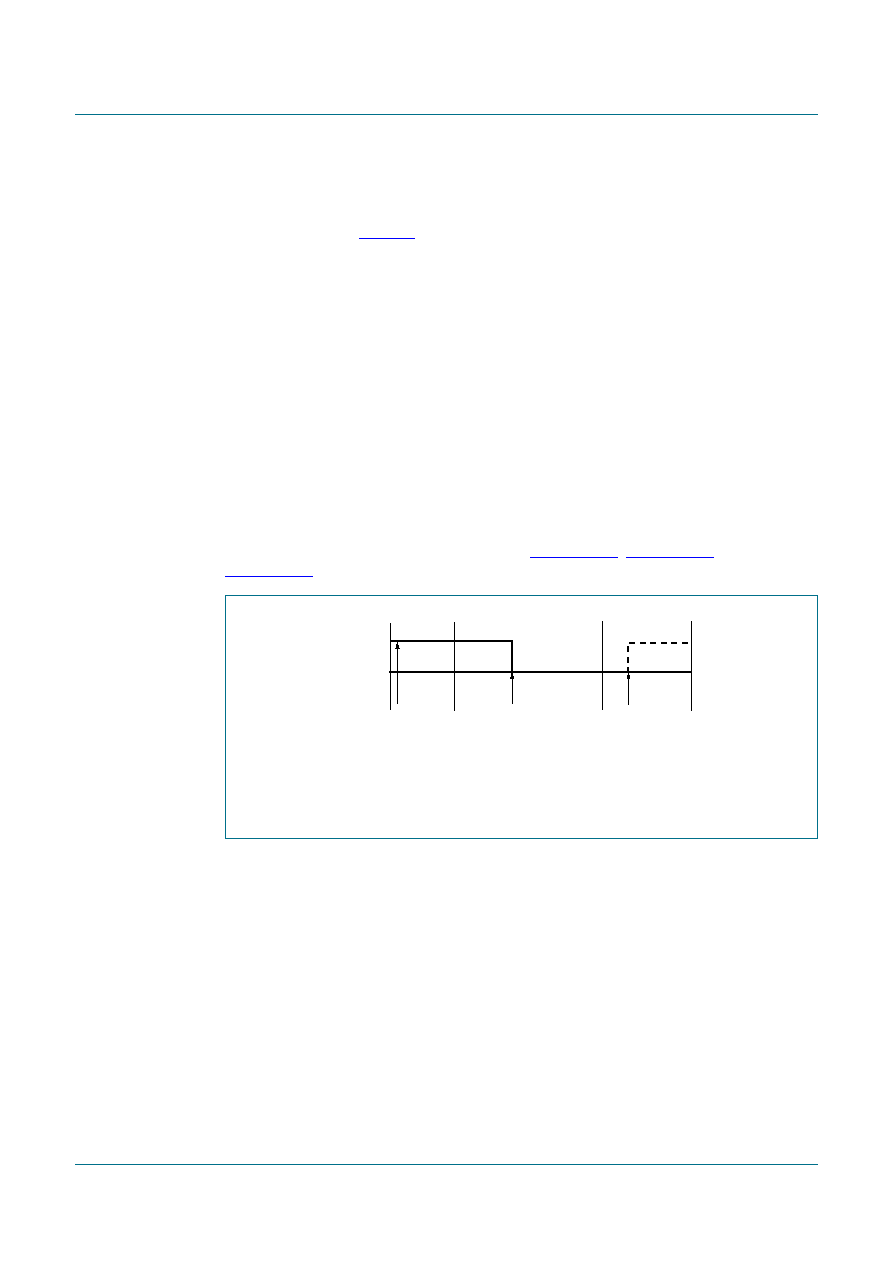

8.13.2 Interrupt control

Bit GLINTENA in the Mode register is a global interrupt enable or disable bit. The behavior

of this bit is given in Figure 6.

The following illustrations are only applicable for level trigger.

Event A: When an interrupt event occurs (for example, SOF interrupt) with bit GLINTENA

set to logic 0, an interrupt will not be generated at pin INT. It will, however, be registered in

the corresponding Interrupt register bit.

Event B: When bit GLINTENA is set to logic 1, pin INT is asserted because bit SOF in the

Interrupt register is already set.

Event C: If the rmware sets bit GLINTENA to logic 0, pin INT will still be asserted. The

bold line shows the desired behavior of pin INT.

Deassertion of pin INT can be achieved either by clearing all the bits in the Interrupt

register or the DMA Interrupt Reason register, depending on the event.

Remark: When clearing an interrupt event, perform write to all the bytes of the register.

For more information on interrupt control, see Section 9.2.2, Section 9.2.5 and

8.14 VBUS sensing

The VBUS pin is one of the ways to wake up the clock when the ISP1583 is suspended

with bit CLKAON set to logic 0 (clock off option).

To detect whether the host is connected or not, that is VBUS sensing, a 1 M resistor and

a 1

F electrolytic or tantalum capacitor must be added to damp the overshoot on plug in.

Pin INT: HIGH = deassert; LOW = assert (individual interrupts are enabled).

Fig 6.

Behavior of bit GLINTENA

INT pin

004aaa394

GLINTENA = 0

SOF asserted

GLINTENA = 1

SOF asserted

GLINTENA = 0

(during this time,

an interrupt event

occurs, for example,

SOF asserted)

A

B

C

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ISP1583BS,551 | UNIVERSAL SERIAL BUS CONTROLLER, PQCC64 |

| ISP1583ET2 | UNIVERSAL SERIAL BUS CONTROLLER, PBGA64 |

| ISP1761ET,518 | UNIVERSAL SERIAL BUS CONTROLLER, PBGA128 |

| ISP1761BE,518 | UNIVERSAL SERIAL BUS CONTROLLER, PQFP128 |

| ISP1761BE,551 | UNIVERSAL SERIAL BUS CONTROLLER, PQFP128 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ISP1583ET1-T | 功能描述:外圍驅(qū)動器與原件 - PCI USB 2.0 SM FTPRINT RoHS:否 制造商:PLX Technology 工作電源電壓: 最大工作溫度: 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FCBGA-1156 封裝:Tray |

| ISP1583ET1TM | 制造商:STMicroelectronics 功能描述: |

| ISP1583ET2 | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:Hi-Speed USB peripheral controller |

| ISP1583ET2,518 | 功能描述:外圍驅(qū)動器與原件 - PCI USB 2.0 DEVICE RoHS:否 制造商:PLX Technology 工作電源電壓: 最大工作溫度: 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FCBGA-1156 封裝:Tray |

| ISP1583ET2-T | 功能描述:外圍驅(qū)動器與原件 - PCI USB 2.0 DEVICE RoHS:否 制造商:PLX Technology 工作電源電壓: 最大工作溫度: 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FCBGA-1156 封裝:Tray |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。