- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄67723 > ISP1583ET1,118 (ST-ERICSSON) UNIVERSAL SERIAL BUS CONTROLLER, PBGA64 PDF資料下載

參數(shù)資料

| 型號: | ISP1583ET1,118 |

| 廠商: | ST-ERICSSON |

| 元件分類: | 總線控制器 |

| 英文描述: | UNIVERSAL SERIAL BUS CONTROLLER, PBGA64 |

| 封裝: | 4 X 4 MM, 0.80 MM HEIGHT, LEAD FREE, PLASTIC, SOT969-1,TFBGA-64 |

| 文件頁數(shù): | 5/100頁 |

| 文件大小: | 508K |

| 代理商: | ISP1583ET1,118 |

第1頁第2頁第3頁第4頁當(dāng)前第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁

ISP1583_7

NXP B.V. 2008. All rights reserved.

Product data sheet

Rev. 07 — 22 September 2008

11 of 99

NXP Semiconductors

ISP1583

Hi-Speed USB peripheral controller

[1]

Symbol names ending with underscore N, for example, NAME_N, represent active LOW signals.

[2]

All outputs and I/O pins can source 4 mA, unless otherwise specied.

[3]

Control signals are not 3-stated.

[4]

Add a decoupling capacitor (0.1

F) to all the supply pins. For better EMI results, add a 0.01 F capacitor in parallel to 0.1 F.

[5]

The DMA bus is in 3-state until a DMA command (see Section 9.4.1) is executed.

BUS_

CONF/

DA0[3]

62

B2

A3

I/O

Bus conguration input — Selects bus mode during

power-up:

LOW: split bus mode; multiplexed 8-bit address and

data bus on AD[7:0], separate DMA data bus

DATA[15:0][5]

HIGH (connect to VCC(I/O)): generic processor mode;

separate 8-bit address on AD[7:0], 16-bit processor

data bus on DATA[15:0]; DMA is multiplexed on

processor bus DATA[15:0]

Address selection output — Selects the Task File

register of an ATA/ATAPI device at normal operation; see

bidirectional pad; 10 ns slew-rate control; TTL; 5 V tolerant

WAKEUP

63

A2

B2

I

wake-up input; when this pin is at the HIGH level, the chip

is prevented from going into the suspend state and

wake-up the chip when already in suspend mode; when

not in use, connect this pin to ground through a 10 k

resistor

When the RESET_N pin is LOW, ensure that the WAKEUP

pin does not go from LOW to HIGH; otherwise the device

will enter test mode.

input pad; TTL; 5 V tolerant

SUSPEND 64

C2

A2

O

suspend state indicator output; used as a power switch

control output to power-off or power-on external devices

when going into suspend mode or recovering from

suspend mode

CMOS output; 8 mA drive

DGND

-

B9

-

digital ground

DGND

exposed die

pad

J9

B8, G7

-

ground supply; down bonded to the exposed die pad (heat

sink); to be connected to DGND during the PCB layout

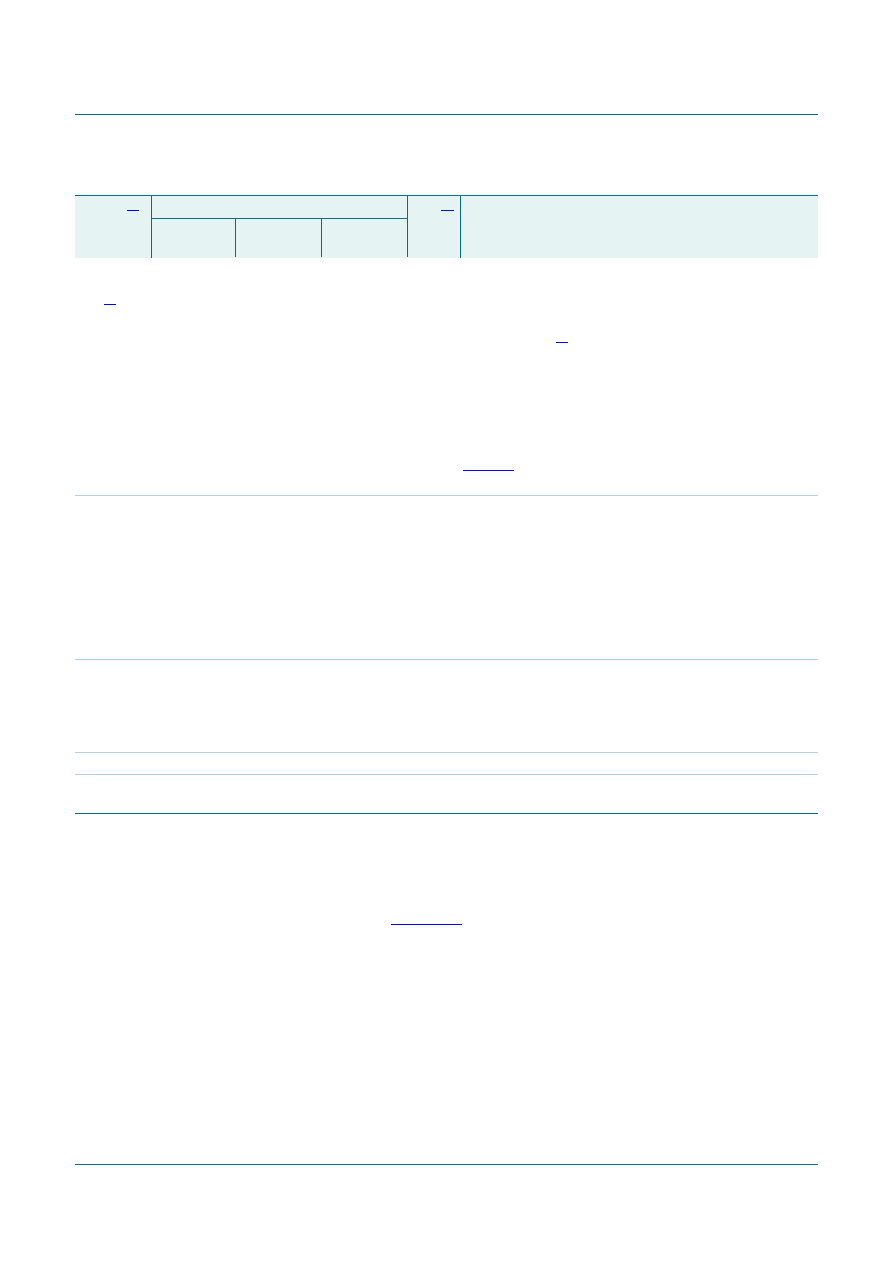

Table 3.

Pin description …continued

Symbol[1]

Pin

Type[2] Description

ISP1583BS ISP1583ET;

ISP1583ET2

ISP1583ET1

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ISP1583BS,551 | UNIVERSAL SERIAL BUS CONTROLLER, PQCC64 |

| ISP1583ET2 | UNIVERSAL SERIAL BUS CONTROLLER, PBGA64 |

| ISP1761ET,518 | UNIVERSAL SERIAL BUS CONTROLLER, PBGA128 |

| ISP1761BE,518 | UNIVERSAL SERIAL BUS CONTROLLER, PQFP128 |

| ISP1761BE,551 | UNIVERSAL SERIAL BUS CONTROLLER, PQFP128 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ISP1583ET1-T | 功能描述:外圍驅(qū)動器與原件 - PCI USB 2.0 SM FTPRINT RoHS:否 制造商:PLX Technology 工作電源電壓: 最大工作溫度: 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FCBGA-1156 封裝:Tray |

| ISP1583ET1TM | 制造商:STMicroelectronics 功能描述: |

| ISP1583ET2 | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:Hi-Speed USB peripheral controller |

| ISP1583ET2,518 | 功能描述:外圍驅(qū)動器與原件 - PCI USB 2.0 DEVICE RoHS:否 制造商:PLX Technology 工作電源電壓: 最大工作溫度: 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FCBGA-1156 封裝:Tray |

| ISP1583ET2-T | 功能描述:外圍驅(qū)動器與原件 - PCI USB 2.0 DEVICE RoHS:否 制造商:PLX Technology 工作電源電壓: 最大工作溫度: 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FCBGA-1156 封裝:Tray |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。