- 您現(xiàn)在的位置:買賣IC網 > PDF目錄373157 > KM48S2020C (SAMSUNG SEMICONDUCTOR CO. LTD.) 1M x 8Bit x 2 Banks Synchronous DRAM(1M x 8位 x 2組同步動態(tài)RAM) PDF資料下載

參數(shù)資料

| 型號: | KM48S2020C |

| 廠商: | SAMSUNG SEMICONDUCTOR CO. LTD. |

| 英文描述: | 1M x 8Bit x 2 Banks Synchronous DRAM(1M x 8位 x 2組同步動態(tài)RAM) |

| 中文描述: | 1M × 8位× 2銀行同步DRAM(1米× 8位× 2組同步動態(tài)RAM)的 |

| 文件頁數(shù): | 31/44頁 |

| 文件大小: | 605K |

| 代理商: | KM48S2020C |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁當前第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁

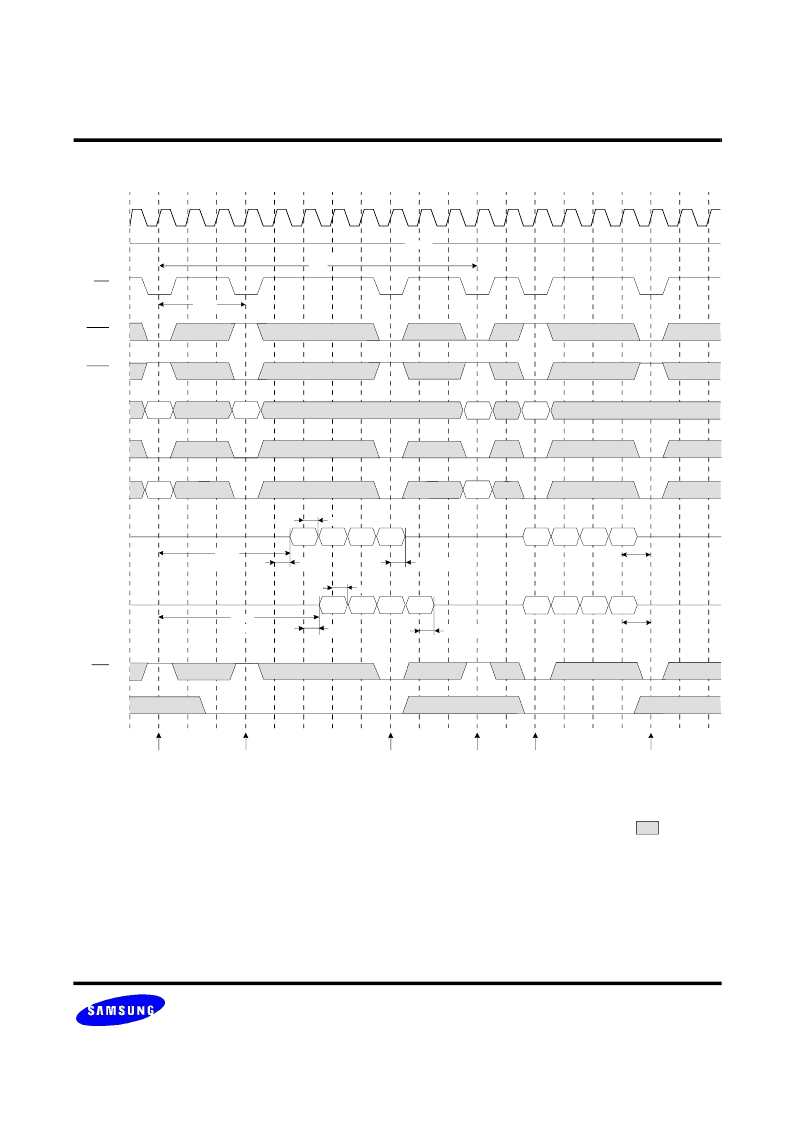

TIMING DIAGRAM - I

CMOS SDRAM

ELECTRONICS

REV. 4 Nov. '97

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

Read & Write Cycle at Same Bank @Burst Length=4

HIGH

Row Active

(A-Bank)

Precharge

(A-Bank)

Row Active

(A-Bank)

Write

(A-Bank)

Precharge

(A-Bank)

: Don't care

*Note :

1. Minimum row cycle times is required to complete internal DRAM operation.

2. Row precharge can interrupt burst on any cycle. [CAS Latency - 1] number of valid output data

is available after Row precharge. Last valid output will be Hi-Z(t

3. Access time from Row active command. t

4. Ouput will be Hi-Z after the end of burst. (1, 2, 4, 8 & Full page bit burst)

SHZ

) after the clcok.

CC

*(t

RCD

+ CAS latency - 1) + t

SAC

Read

(A-Bank)

*Note 1

tRC

tRCD

*Note 2

tRDL

tRDL

tSHZ

*Note 4

tSHZ

*Note 4

tOH

tRAC

*Note 3

tSAC

tSAC

tRAC

*Note 3

tOH

BA

A

10

/AP

CL=2

CL=3

DQ

ADDR

CAS

RAS

CS

CKE

CLOCK

Ra

Rb

Qa0

Qa1

Qa2

Qa3

Qa0

Qa1

Qa2

Qa3

Db0

Db1

Db2

Db3

Db0

Db1

Db2

Db3

Ra

Ca0

Rb

Cb0

WE

DQM

相關PDF資料 |

PDF描述 |

|---|---|

| KM48S8020B | 4M x 8Bit x 2 Banks Synchronous DRAM(4M x 8位 x 2組同步動態(tài)RAM) |

| KM48S8030D | 64Mbit SDRAM 2M x 8Bit x 4 Banks Synchronous DRAM LVTTL |

| KM48S8030 | 2M x 8Bit x 4 Banks Synchronous DRAM |

| KM48S8030C | 2M x 8Bit x 4 Banks Synchronous DRAM |

| KM48V2004C | 2M x 8Bit CMOS Dynamic RAM with Extended Data Out(2M x 8位CMOS 動態(tài)RAM(帶擴展數(shù)據輸出)) |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| KM48S2020CT-G10 | 制造商:Samsung Semiconductor 功能描述: |

| KM48S8020AT-G10 | 制造商:Samsung Electro-Mechanics 功能描述:SDRAM, 2x 4Mx 8, 54 Pin, Plastic, TSOP |

| KM48S8030 | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:2M x 8Bit x 4 Banks Synchronous DRAM |

| KM48S8030C | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:2M x 8Bit x 4 Banks Synchronous DRAM |

| KM48S8030CT-G/FA | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:2M x 8Bit x 4 Banks Synchronous DRAM |

發(fā)布緊急采購,3分鐘左右您將得到回復。