- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄367612 > LU3X31T-T64 LU3X31T-T64 Single-Port 3 10/100 Ethernet Transceiver TX PDF資料下載

參數(shù)資料

| 型號: | LU3X31T-T64 |

| 英文描述: | LU3X31T-T64 Single-Port 3 10/100 Ethernet Transceiver TX |

| 中文描述: | LU3X31T - T64單端口10/100以太網(wǎng)收發(fā)器3得克薩斯州 |

| 文件頁數(shù): | 7/44頁 |

| 文件大?。?/td> | 580K |

| 代理商: | LU3X31T-T64 |

第1頁第2頁第3頁第4頁第5頁第6頁當(dāng)前第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁

Lucent Technologies Inc.

7

Preliminary Data Sheet

July 2000

LU3X31T-T64 Single-Port 3 V

10/100 Ethernet Transceiver TX

Pin Descriptions

(continued)

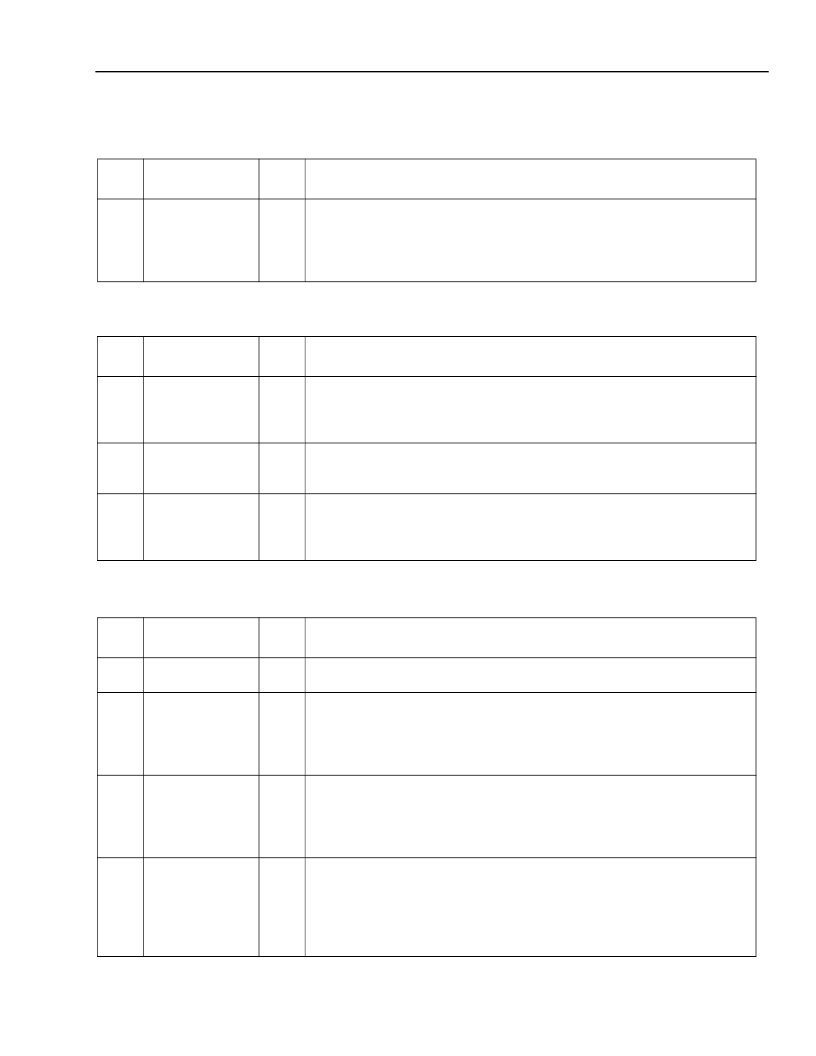

Table 4. PHY Address Configuration

Note: Smaller font indicates that the pin has multiple functions.

Table 5. 100Base-X PCS Configuration

Note: Smaller font indicates that the pin has multiple functions.

Table 6. Autonegotiation Configuration

(Refer to Table 11.)

Pin

No.

10

12

16

34

39

Pin Name

I/O

Pin Description

PHY[0]

PHY[1]

PHY[2]/

MDIOINTZ

PHY[3]/

CRS

PHY[4]/

COL

I

I

I/O

I/O

I/O

PHY Address[4:0].

These 5 pins are detected during powerup or reset to

initialize the PHY address used for MII management register interface. PHY

address 00h forces the PHY into MII isolate mode. PHY address pins[4:2]

have an internal 40 k

pull-down resistor. See Table 3 for MDIOINTZ, CRS,

and COL description.

Pin

No.

41

Pin Name

I/O

Pin Description

BPSCR/

LEDTX

/

ACTLED

I/O

Bypass Scrambler Mode.

A high value on this pin during powerup or reset

will bypass the scramble/descramble operations in 100Base-X data path.

This pin has an internal 40 k

pull-down resistor. See Table 7 for LEDTX/

ACTLED description.

Bypass 4B/5B Mode.

A high value on this pin during powerup or reset will

bypass the 4B/5B encoder of the PHY. This pin has an internal 40 k

pull-

down resistor. See Table 7 for LEDCOL description.

Bypass Alignment Mode.

A high value on this pin during powerup or reset

will bypass the alignment feature of the PHY. This bypass mode provides a

symbol interface. This pin has an internal 40 k

pull-down. See Table 7 for

LNKLED description.

42

BP4B5B/

LEDCOL

I/O

44

BPALIGN/

LNKLED

I/O

Pin

No.

4

Pin Name

I/O

Pin Description

AUTONEN

I

Autonegotiation Enable.

A high value on this pin during powerup or reset

will enable autonegotiation; a low value will disable it.

100 Full-Duplex Enable.

The logic level of this pin is detected at powerup

or reset to determine whether 100 Mbits/s full-duplex mode is available.

When autonegotiation is enabled, this input sets the ability register bit in

advertisement register 4. When autonegotiation is not enabled, this input

will select the mode of operation.

100 Half-Duplex Enable.

The logic level of this pin is detected at powerup

or reset to determine whether 100 Mbits/s half-duplex mode is available.

When autonegotiation is enabled, this input sets the ability register bit in

advertisement register 4. When autonegotiation is not enabled, this input

will select the mode of operation.

10 Full-Duplex Enable.

The logic level of this pin is detected at

powerup or reset to determine whether 10 Mbits/s full-duplex mode is avail-

able. When autonegotiation is enabled, this input sets the ability register bit

in advertisement register 4. When autonegotiation is not enabled, this input

will select the mode of operation. This pin has an internal 40 k

pull-up

resistor. See Table 7 for LEDSP description.

2

100FDEN

I

11

100HDEN

I

17

10FDEN/

LEDSP

I/O

Note: Smaller font indicates that the pin has multiple functions.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| LU3X31T-T64 | Single-Port 3 V 10/100 Ethernet Transceiver TX/FX(單端口 3 V 10M位和100M位以太網(wǎng)收發(fā)器) |

| LU59002 | Consumer IC |

| LU6612 | LU6612 FASTCAT TM Single-FET for 10Base-T/100Base-TX |

| LU6612-T64-DB | LU6612 FASTCAT TM Single-FET for 10Base-T/100Base-TX |

| LU6612 | Single-FET for 10Base-T/100Base-TX(應(yīng)用于10基數(shù)-T和100基數(shù)-TX 的單快速以太網(wǎng)收發(fā)器) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| LU3X34FTR | 制造商:AGERE 制造商全稱:AGERE 功能描述:Quad 3 V 10/100 Ethernet Transceiver TX/FX |

| LU3X34FTR-HS128-DB | 制造商:AGERE 制造商全稱:AGERE 功能描述:Quad 3 V 10/100 Ethernet Transceiver TX/FX |

| LU3X54FT | 制造商:AGERE 制造商全稱:AGERE 功能描述:QUAD-FET (Fast Ethernet Transceiver) for 10Base-T/100Base-TX/FX |

| LU3X54FTL | 制造商:AGERE 制造商全稱:AGERE 功能描述:QUAD-FET for 10Base-T/100Base-TX/FX |

| LU3X54FTLHS208 | 制造商:Alcatel-Lucent 功能描述:3X54FTLHS208 |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。