- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄359154 > MCIMX27 (飛思卡爾半導(dǎo)體(中國)有限公司) Multimedia Applications Processor(多媒體應(yīng)用處理器) PDF資料下載

參數(shù)資料

| 型號(hào): | MCIMX27 |

| 廠商: | 飛思卡爾半導(dǎo)體(中國)有限公司 |

| 英文描述: | Multimedia Applications Processor(多媒體應(yīng)用處理器) |

| 中文描述: | 多媒體應(yīng)用處理器(多媒體應(yīng)用處理器) |

| 文件頁數(shù): | 55/118頁 |

| 文件大小: | 1159K |

| 代理商: | MCIMX27 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁當(dāng)前第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁

Signal Descriptions

i.MX27 Data Sheet, Advance Information, Rev. 0.1

Freescale Semiconductor

Preliminary—Subject to Change Without Notice

55

3.5.7

Direct Memory Access Controller (DMAC)

After assertion of External DMA Request the DMA burst will start when the corresponding DMA channel

becomes the current highest priority channel. The External DMA Request should be kept asserted until it

is serviced by the DMAC. One External request will initiate at least one DMA burst.

The output External Grant signal from the DMAC is an active-low signal. This signal will be asserted

during the time when a DMA burst is ongoing for an External DMA Request, when the following

conditions are true:

The DMA channel for which the DMA burst is ongoing has requested source as external DMA

Request (as per RSSR settings).

REN and CEN bit of this channel are set.

External DMA Request is asserted.

Once the grant is asserted the External DMA Request will not be sampled until completion of the DMA

burst. The priority of the external request will become low, for the next consecutive burst, if another DMA

request signal is asserted.

The waveforms are shown for the worst case—that is, smallest burst (1 byte read/write). Minimum and

maximum timings for the External request and External grant signal are present in the data sheet.

Figure 15

shows the minimum time for which the External Grant signal remains asserted if External DMA

request is de-asserted immediately after sensing grant signal active.

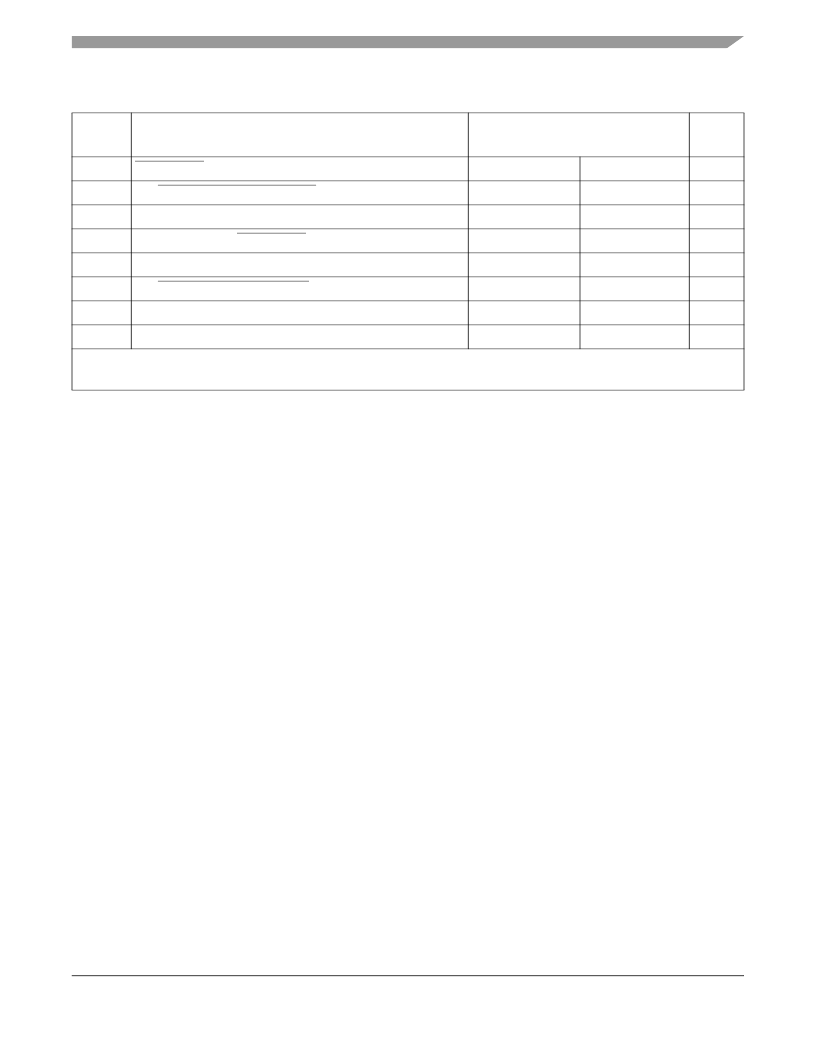

Table 22. CSPI Interface Timing Parameters

Num

Characteristic

3.3 V

Unit

1

CSPI1_RDY to SSn output low

—

—

ns

2

SSn output low to first SCLK edge

2T

—

ns

3

Last SCLK edge to SSn output high

2T

—

ns

4

SSn output high to CSPI1_RDY low

0

—

ns

5

SSn output width

2T + WAIT

—

ns

6

SSn input low to first SCLK edge

—

—

ns

7

SSn input pulse width

0

—

ns

8

pause between data word

0

—

ns

Note:

T

= CSPI clock period

Note:

WAIT = Number of bit clocks or 32.768 kHz clocks as per the Sample Period Control Register value.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MCIMX31_07 | Multimedia Applications Processors |

| MCIMX31 | Multimedia Applications Processors |

| MCL245 | SILICON EPITAXIAL PLANAR DIODE |

| MCL908QT1 | M68HC08 Microcontrollers |

| MCM63R836 | MCM63R836 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MCIMX27_08 | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:Multimedia Applications Processor |

| MCIMX27ADSE | 功能描述:開發(fā)板和工具包 - ARM I.MX27 ADS RoHS:否 制造商:Arduino 產(chǎn)品:Development Boards 工具用于評(píng)估:ATSAM3X8EA-AU 核心:ARM Cortex M3 接口類型:DAC, ICSP, JTAG, UART, USB 工作電源電壓:3.3 V |

| MCIMX27ADSE | 制造商:Freescale Semiconductor 功能描述:Development Kit |

| MCIMX27EC | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:Multimedia Applications Processor |

| MCIMX27IPCAM | 功能描述:視頻 IC 開發(fā)工具 I.MX27 IP CAMERA REF RoHS:否 制造商:Texas Instruments 產(chǎn)品:Evaluation Boards 類型:YPbPr to RGBHV Converters 工具用于評(píng)估:LMH1251 工作電源電壓:5 V |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。