- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄383644 > MT9074 (Mitel Networks Corporation) T1/E1/J1 Single Chip Transceiver PDF資料下載

參數(shù)資料

| 型號(hào): | MT9074 |

| 廠商: | Mitel Networks Corporation |

| 英文描述: | T1/E1/J1 Single Chip Transceiver |

| 中文描述: | T1/E1/J1收發(fā)單芯片收發(fā)器 |

| 文件頁(yè)數(shù): | 101/122頁(yè) |

| 文件大小: | 372K |

| 代理商: | MT9074 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)第94頁(yè)第95頁(yè)第96頁(yè)第97頁(yè)第98頁(yè)第99頁(yè)第100頁(yè)當(dāng)前第101頁(yè)第102頁(yè)第103頁(yè)第104頁(yè)第105頁(yè)第106頁(yè)第107頁(yè)第108頁(yè)第109頁(yè)第110頁(yè)第111頁(yè)第112頁(yè)第113頁(yè)第114頁(yè)第115頁(yè)第116頁(yè)第117頁(yè)第118頁(yè)第119頁(yè)第120頁(yè)第121頁(yè)第122頁(yè)

Advance Information

MT9074

101

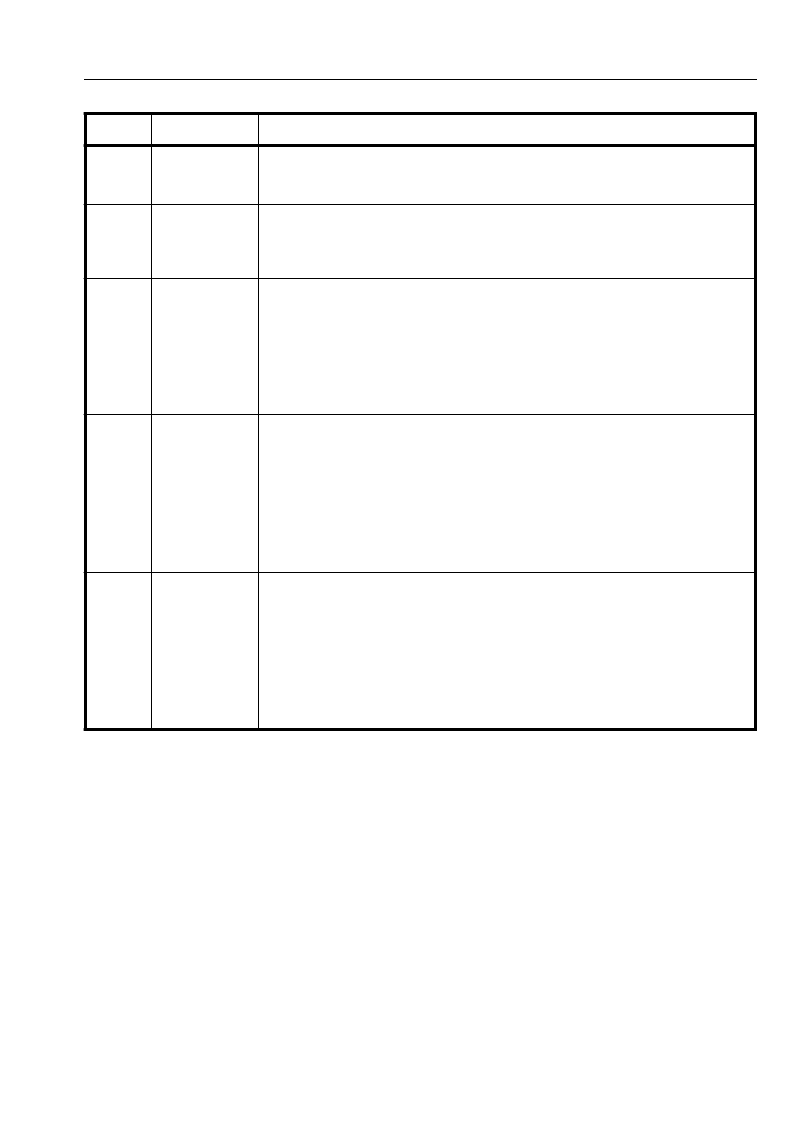

Bit

Name

Functional Description

7

INTGEN

Interrupt Generated. Set to 1 when an interrupt (in conjunction with the Interrupt

Mask Register) has been generated by the HDLC. This is an asynchronous event.

It is reset when the interrupt Register is read.

6

Idle Chan

Idle Channel. Set to a 1 when an idle Channel state (15 or more ones) has been

detected at the receiver. This is an asynchronous event. On power reset, this may

be 1 if the clock (RXC) was not operating. Status becomes valid after the first 15

bits or the first zero is received.

5 - 4

RQ9, RQ8

Byte Status bits from RX FIFO. These bits determine the status of the byte to be

read from RX FIFO as follows:

RQ9 RQ8 Byte Status

0 0 Packet Byte

0 1 First Byte

1 0 Last byte of a good packet.

1 1 Last byte of a bad packet.

3 - 2

TxSTAT2-1

These bits determine the status of the TX FIFO as follows:

TxSTAT2 TxSTAT1 TX FIFO Status

0 0 TX FIFO full up to the selected status level or more.

0 1 The number of bytes in the TX FIFO has reached or

exceeded the selected interrupt threshold level.

1 0 TX FIFO empty.

1 1 The number of bytes in the TX FIFO is less than the

selected interrupt threshold level.

1 - 0

RxSTAT2 - 1

These bits determine the status of the RX FIFO as follows:

RxSTAT2 RxSTAT1 RX FIFO Status

0 0 RX FIFO empty

0 1 The number of bytes in the RX FIFO is less

than the interrupt threshold level.

1 0 RX FIFO full.

1 1 The number of bytes in the RX FIFO has reached or

exceeded the interrupt threshold level.

Table 145 - HDLC Status Register

(Page B & C Address 14H)

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MT9074AL | T1/E1/J1 Single Chip Transceiver |

| MT9074AP | T1/E1/J1 Single Chip Transceiver |

| MT9074 | T1/E1/J1 Single Chip Transceiver(T1/E1/J1單片收發(fā)器) |

| MT9075B | E1 Single Chip Transceiver |

| MT9075B | E1 Single Chip Transceiver(E1單片收發(fā)器) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MT9074_05 | 制造商:ZARLINK 制造商全稱(chēng):Zarlink Semiconductor Inc 功能描述:T1/E1/J1 Single Chip Transceiver |

| MT9074AL | 制造商:Microsemi Corporation 功能描述:FRAMER E1/J1/T1 5V 100MQFP - Trays 制造商:Zarlink Semiconductor Inc 功能描述:FRAMER E1/J1/T1 5V 100MQFP - Trays |

| MT9074AL1 | 制造商:Microsemi Corporation 功能描述:FRAMER E1/J1/T1 5V 100MQFP - Trays |

| MT9074AP | 制造商:Microsemi Corporation 功能描述: |

| MT9074AP1 | 制造商:Microsemi Corporation 功能描述:T1/E1/J1 SGLE CHIP XSCR 制造商:Microsemi Corporation 功能描述:FRAMER E1/J1/T1 5V 68PLCC - Rail/Tube 制造商:MICROSEMI CONSUMER MEDICAL PRODUCT GROUP 功能描述:IC TXRX SGL T1/E1 68PLCC 制造商:Microsemi Corporation 功能描述:IC TXRX SGL T1/E1 68PLCC |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。