- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄383645 > MT9076 (Mitel Networks Corporation) T1/E1/J1 3.3V Single Chip Transceiver PDF資料下載

參數(shù)資料

| 型號(hào): | MT9076 |

| 廠商: | Mitel Networks Corporation |

| 英文描述: | T1/E1/J1 3.3V Single Chip Transceiver |

| 中文描述: | T1/E1/J1收發(fā)3.3V的單芯片收發(fā)器 |

| 文件頁(yè)數(shù): | 5/160頁(yè) |

| 文件大小: | 416K |

| 代理商: | MT9076 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)當(dāng)前第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)第94頁(yè)第95頁(yè)第96頁(yè)第97頁(yè)第98頁(yè)第99頁(yè)第100頁(yè)第101頁(yè)第102頁(yè)第103頁(yè)第104頁(yè)第105頁(yè)第106頁(yè)第107頁(yè)第108頁(yè)第109頁(yè)第110頁(yè)第111頁(yè)第112頁(yè)第113頁(yè)第114頁(yè)第115頁(yè)第116頁(yè)第117頁(yè)第118頁(yè)第119頁(yè)第120頁(yè)第121頁(yè)第122頁(yè)第123頁(yè)第124頁(yè)第125頁(yè)第126頁(yè)第127頁(yè)第128頁(yè)第129頁(yè)第130頁(yè)第131頁(yè)第132頁(yè)第133頁(yè)第134頁(yè)第135頁(yè)第136頁(yè)第137頁(yè)第138頁(yè)第139頁(yè)第140頁(yè)第141頁(yè)第142頁(yè)第143頁(yè)第144頁(yè)第145頁(yè)第146頁(yè)第147頁(yè)第148頁(yè)第149頁(yè)第150頁(yè)第151頁(yè)第152頁(yè)第153頁(yè)第154頁(yè)第155頁(yè)第156頁(yè)第157頁(yè)第158頁(yè)第159頁(yè)第160頁(yè)

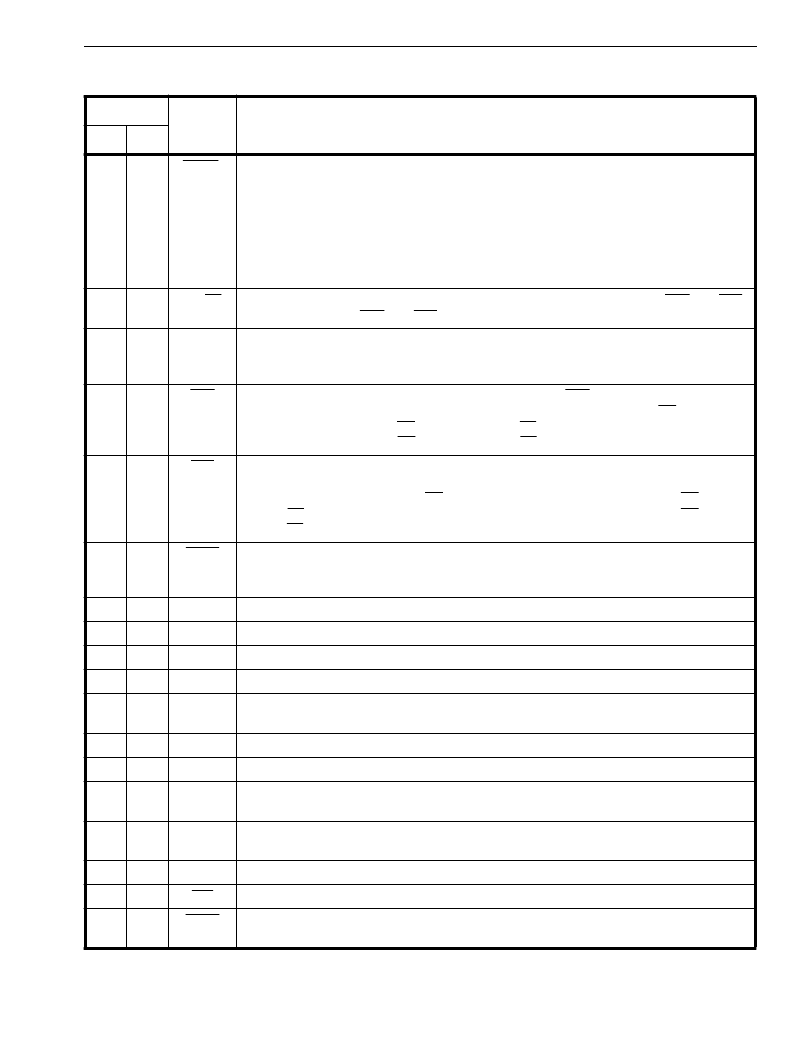

Preliminary Information

MT9076

5

42

17

RxMF/

TxFP

Receive Multiframe Boundary / Transmit Frame Boundary (5V tolerant Output).

If

the control bit Tx8KEN (page 02H address 10H bit 2) is low, this negative output pulse

delimits the received multiframe boundary. The next frame output on the data stream

(DSTo) is basic frame zero on the T1 or PCM 30 link. In E1 mode this receive

multiframe signal can be related to either the receive CRC multiframe (page 01H,

address 17H, bit 6, MFSEL=1) or the receive signaling multiframe (MFSEL=0). If the

control bit Tx8KEN is set high, this positive output pulse delimits the frame boundary

(the first bit transmit in the frame) for the digital output stream on pins TXA and TXB.

43

18

BS/LS

Bus/Line Syncronization Mode Selection (5V tolerant Input)

. If high, C4b and F0b

will be inputs; if low, C4b and F0b will be outputs.

44

22

Exclk

2.048 MHz in E1 mode or 1.544MHz in T1 mode, Extracted Clock (5V tolerant

Output).

The clock extracted from the received signal and used internally to clock in

data received on RTIP and RRING.

45

23

C4b

4.096 MHz System Clock (5V tolerant Input/Output).

C4b is the clock for the ST-BUS

sections and transmit serial PCM data of the MT9076. In the free-run (S/FR/Exclki=0) or

line synchronous mode (S/FR/Exclki=1 and BS/LS=0) this signal is an output, while in

bus synchronous mode (S/FR/Exclki=1 and BS/LS=1) this signal is an input clock.

46

24

F0b

Frame Pulse (5V tolerant Input/Output).

This is the ST-BUS frame synchronization

signal, which delimits the 32 channel frame of CSTi, CSTo, DSTi, DSTo and the

PCM30 link. In the free-run (S/FR/Exclki=0) or line synchronous mode (S/FR/Exclki=1

and BS/LS=0) this signal is an output, while in bus synchronous mode (S/FR/Exclki=1

and BS/LS=1) this signal is an input.

47

25

RxFP

Receive Frame Pulse/Receive CCS Clock (5V tolerant Output).

An 8kHz pulse

signal, which is low for one extracted clock period. This signal is synchronized to the

receive DS1 or PCM 30 basic frame boundary.

48

26

IC1

Internal Connection.

Must be left open for normal operation.

49

27

V

SS2

V

DD2

VDD

ATx

TTIP

TRING

Negative Power Supply.

Digital ground.

50

28

Positive Power Supply.

Digital supply (+3.3V

±

5%).

Transmit Analog Power Supply.

Analog supply for the LIU transmitter (+3.3V

±

5%).

51

29

52

53

30

31

Transmit TIP and RING(Output).

Differential outputs for the transmit line signal - must

be transformer coupled (See Figure 6).

54

32

GND

ATx

Tdi

Transmit Analog Ground .

Analog ground for the LIU transmitter.

55

33

IEEE 1149.1a Test Data Input (3V Input).

If not used, this pin should be pulled high.

56

34

Tdo

IEEE 1149.1a Test Data Output (5V tolerant Output).

If not used, this pin should be

left unconnected.

57

35

Tms

IEEE 1149.1a Test Mode Selection (3V Input)

. If not used, this pin should be pulled

high.

58

36

Tclk

IEEE 1149.1a Test Clock Signal (3V Input).

If not used, this pin should be pulled high.

59

37

Trst

IEEE 1149.1a Reset Signal (3V Input).

If not used, this pin should be held low.

60

38

TxAO

Transmit All Ones (Input).

High - TTIP, TRING will transmit data normally. Low - TTIP,

TRING will transmit an all ones signal.

Pin Description (continued)

Pin #

Name

Description

PLCC LQFP

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MT9076AB | T1/E1/J1 3.3V Single Chip Transceiver |

| MT9076 | T1/E1/J1 3.3V Single Chip Transceiver(T1/E1/J1 3.3V 單片收發(fā)器) |

| MT9079 | Advanced Controller for E1(先進(jìn)的E1幀調(diào)節(jié)器和控制器) |

| MT9080B | SMX - Switch Matrix Module(用于消費(fèi)類轉(zhuǎn)換應(yīng)用的開關(guān)矩陣模塊) |

| MT90810 | Flexible MVIP(Multi-Vendor Integration Protocol) Interface Circuit(彈性MVIP接口電路) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MT9076AB | 制造商:MITEL 制造商全稱:Mitel Networks Corporation 功能描述:T1/E1/J1 3.3V Single Chip Transceiver |

| MT9076AP | 制造商:MITEL 制造商全稱:Mitel Networks Corporation 功能描述:T1/E1/J1 3.3V Single Chip Transceiver |

| MT9076B | 制造商:ZARLINK 制造商全稱:Zarlink Semiconductor Inc 功能描述:T1/E1/J1 3.3 V Single Chip Transceiver |

| MT9076BB | 制造商:Zarlink Semiconductor Inc 功能描述:FRAMER E1/J1/T1 3.3V 80LQFP - Trays |

| MT9076BB1 | 制造商:Zarlink Semiconductor Inc 功能描述:FRAMER E1/J1/T1 3.3V 80LQFP - Trays |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。