- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄368349 > PT7D6555 -40V Single P-Channel HEXFET Power MOSFET in a TSOP-6 (Micro 6) package PDF資料下載

參數(shù)資料

| 型號(hào): | PT7D6555 |

| 英文描述: | -40V Single P-Channel HEXFET Power MOSFET in a TSOP-6 (Micro 6) package |

| 中文描述: | 擴(kuò)展的PCM接口控制器? |

| 文件頁(yè)數(shù): | 29/56頁(yè) |

| 文件大?。?/td> | 489K |

| 代理商: | PT7D6555 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)當(dāng)前第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

Preliminary Data Sheet

PT7D6555

Extended PCM Interface Controller

29

PT0105(08/02)

Ver:0

Configurable Interface Registers

Configurable Interface Mode Register 1 (CMD1)

Value after reset: 00000000B

Address: 2CH(1/6H)

Read/Write

7 0

CSS

CSM

CSP1

CSP0

CMD1 CMD0 CIS1

CIS0

CSS

Clock Source Selection.

0

…

PDC and PFS are used as clock and framing source for the CFI. Clock and framing signals derived from these

sources are output on DCL and FSC.

1

…

DCL and FSC are selected as clock and framing source for the CFI.

CSM

CFI-Synchronization Mode.

The rising FSC edge synchronizes the CFI-frame.

0

…

FSC is evaluated with every falling edge of DCL.

1

…

FSC is evaluated with every rising edge of DCL.

Note:

If CSS = 0 is selected, CSM and PMOD: PSM must be programmed identical.

CSP1..0

Clock Source Prescaler 1,0.

The clock source frequency is divided according to the following table to obtain the CFI reference clock CRCL.

CSP1,0

00

01

10

11

Prescaler Divisor

2

1.5

1

Not allowed

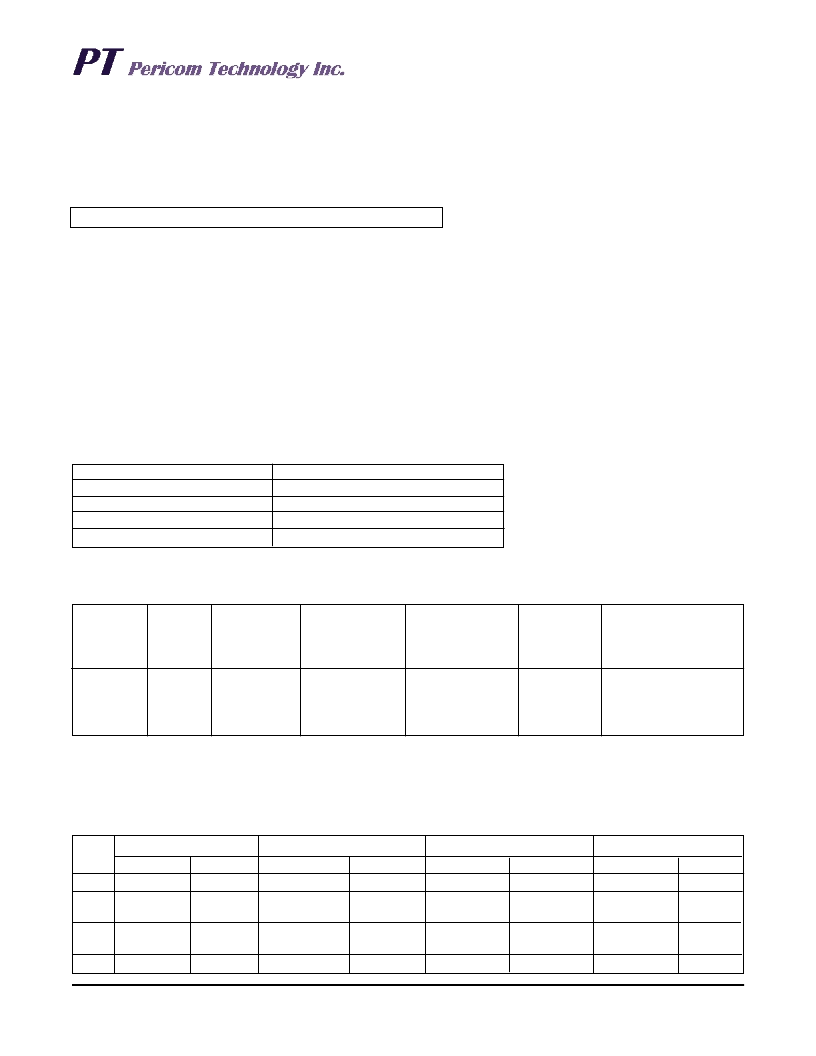

CMD1..0

CFI Mode1, 0.

Defines the actual number and configuration of the CFI ports.

CMD1..0

CFI

Number of

Mode

Logical Ports

CFI Data Rate

[kbit/s]

Min.

Min. Required

CFI Data Rate

[kbit/s] Relative Clock (RCL) CMD1: CSS0=0

to PCM-Data Rate

32N/3

2xDR

64N/3

DR

64N/3

0.5xDR

16N/3

4xDR

Necessary

Reference

DCL-Output

Frequencies

Max.

00

01

10

11

Note

: N = number of time slots in a PCM frame

0

1

2

3

4 DU (0..3)

2 DU (0..1)

1 DU

8 bid (0..7)

128

128

128

128

2048

4096

8192

1024

DR, 2xDR

DR

DR

DR, 2xDR

CIS1..0

CFI Alternative Input Selection.

In CFI mode 1 and 2 CIS1..0 controls the assignment between logical and physical receive pins. In CFI mode 0 and

3 CIS1,0 should be set to 0.

CFI

Mode

0

1

Port 0

DU0 DD0

IN0 OUT0

IN0 OUT0

CIS0 = 0

IN OUT

CIS0 = 0

I/O4

Port 1

DU1 DD1

IN1 OUT1

IN1 OUT1

CIS1=0

Not active Tristate

Port 2

DU2 DD2

IN2 OUT2

IN0 Tristate

CIS0 =1

IN Tristate

CIS0 =1

I/O6

Port 3

DU3 DD3

IN3 OUT3

IN1 Tristate

CIS1 =1

Not active Tristate

2

3

I/O0

I/O5

I/O1

I/O2

I/O7

I/O3

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| PT7M7803RT | μP Supervisor Circuits? |

| PT7V2727 | 3.3v/5.0v operating voltage |

| PT7V2727W | 3.3v/5.0v operating voltage |

| PT7V3727W | 3.3v/5.0v operating voltage |

| PT7V4027W | 3.3V operating voltage |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| PT7FFSDGY | 制造商:Hubbell Wiring Device-Kellems 功能描述:FLUSH FRPT, 1 SERV, FURN FEED, GY |

| PT7FFSDI | 制造商:Hubbell Wiring Device-Kellems 功能描述:FLUSH FRPT, 1 SERV, FURN FEED, IV |

| PT7FSD | 制造商:Hubbell Wiring Device-Kellems 功能描述:THRU-FLOOR FITTING, 3 FLUSH FRPT |

| PT7FSDBLA | 制造商:Hubbell Wiring Device-Kellems 功能描述:FLUSH FRPT, W/20A DUP/TELE/DATA,BK |

| PT7FSDBRA | 制造商:Hubbell Wiring Device-Kellems 功能描述:FLUSH FRPT, W/20A DUP/TELE/DATA,BR |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。