- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄373631 > TFRA08C13 Ultraframer DS3/E3/DS2/E2/DS1/E1/DS0 PDF資料下載

參數(shù)資料

| 型號: | TFRA08C13 |

| 元件分類: | 通信及網(wǎng)絡(luò) |

| 英文描述: | Ultraframer DS3/E3/DS2/E2/DS1/E1/DS0 |

| 中文描述: | Ultraframer DS3/E3/DS2/E2/DS1/E1/DS0 |

| 文件頁數(shù): | 94/188頁 |

| 文件大小: | 3047K |

| 代理商: | TFRA08C13 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁當前第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁第128頁第129頁第130頁第131頁第132頁第133頁第134頁第135頁第136頁第137頁第138頁第139頁第140頁第141頁第142頁第143頁第144頁第145頁第146頁第147頁第148頁第149頁第150頁第151頁第152頁第153頁第154頁第155頁第156頁第157頁第158頁第159頁第160頁第161頁第162頁第163頁第164頁第165頁第166頁第167頁第168頁第169頁第170頁第171頁第172頁第173頁第174頁第175頁第176頁第177頁第178頁第179頁第180頁第181頁第182頁第183頁第184頁第185頁第186頁第187頁第188頁

94

Lucent Technologies Inc.

TFRA08C13 OCTAL T1/E1 Framer

Preliminary Data Sheet

October 2000

Facility Data Link

(continued)

In the transmit direction, the FDL HDLC takes data

from the transmit FIFO and transmits that data exactly

bit-for-bit on the TFDL interface. Transmit data is octet-

aligned to the first TFDLCK after the transmitter has

been enabled. The bits are transmitted least significant

bit first. When there is no data in the transmit FIFO, the

FDL HDLC either transmits all ones, or transmits the

programmed HDLC transmitter idle character (register

FDL_PR5) if register FDL_PR9 bit 6 (FMATCH) is set

to 1. To cause the transmit idle character to be sent

first, the character must be programmed before the

transmitter is enabled.

The transmitter empty interrupt, register FDL_SR0 bit 1

(FTEM), acts as in the HDLC mode. The transmitter-

done interrupt, register FDL_SR0 bit 0 (FTDONE), is

used to report an empty FDL transmit FIFO. The

FTDONE interrupt thus provides a way to determine

transmission end. Register FDL_SR0 bit 2 (FTUND-

ABT) interrupt is not active in the transparent mode.

In the receive direction, the FDL HDLC block loads

received data from the RFDL interface directly into the

receive FIFO bit-for-bit. The data is assumed to be

least significant bit first. If FMATCH register FDL_PR9

bit 6 is 0, the receiver begins loading data into the

receive FIFO beginning with the first RFDLCK detected

after the receiver has been enabled. If the FMATCH bit

is set to 1, the receiver does not begin loading data into

the FIFO until the receiver match character has been

detected. The search for the receiver match character

is in a sliding window fashion if register FDL_PR9 bit 4

(FALOCT) bit is 0 (align to octet), or only on octet

boundaries if FALOCT is set to 1. The octet boundary

is aligned relative to the first RFDLCK after the receiver

has been enabled. The matched character and all sub-

sequent bytes are placed in the receive FIFO. An FDL

receiver reset, register FDL_PR1 bit 4 (FRR) = 1,

causes the receiver to realign to the match character if

FMATCH is set to 1.

The receiver full (FRF) and receiver overrun

(FROVERUN) interrupts in register FDL_SR0 act as in

the HDLC mode. The received end of frame (FREOF)

and receiver idle (FRIDL) interrupts are not used in the

transparent mode. The match status (FMSTAT) bit is

set to 1 when the receiver match character is first rec-

ognized. If the FMATCH bit is 0, the FMSTAT

(FDL_PR9 bit 3) bit is set to 1 automatically when the

first bit is received, and the octet offset status bits

(FDL_PR9 bit 0—bit 2) read 000. If the FMATCH bit is

programmed to 1, the FMSTAT bit is set to 1 upon rec-

ognition of the first receiver match character, and the

octet offset status bits indicate the offset relative to the

octet boundary at which the receiver match character

was recognized. The octet offset status bits have no

meaning until the FMSTAT bit is set to 1. An octet offset

of 111 indicates byte alignment.

An interrupt for recognition of the match character can

be generated by setting the FRIL level to 1. Since the

matched character is the first byte written to the FIFO,

the FRF interrupt occurs with the writing of the match

character to the receive FIFO.

The operation of the receiver in transparent mode is

summarized in Table 44.

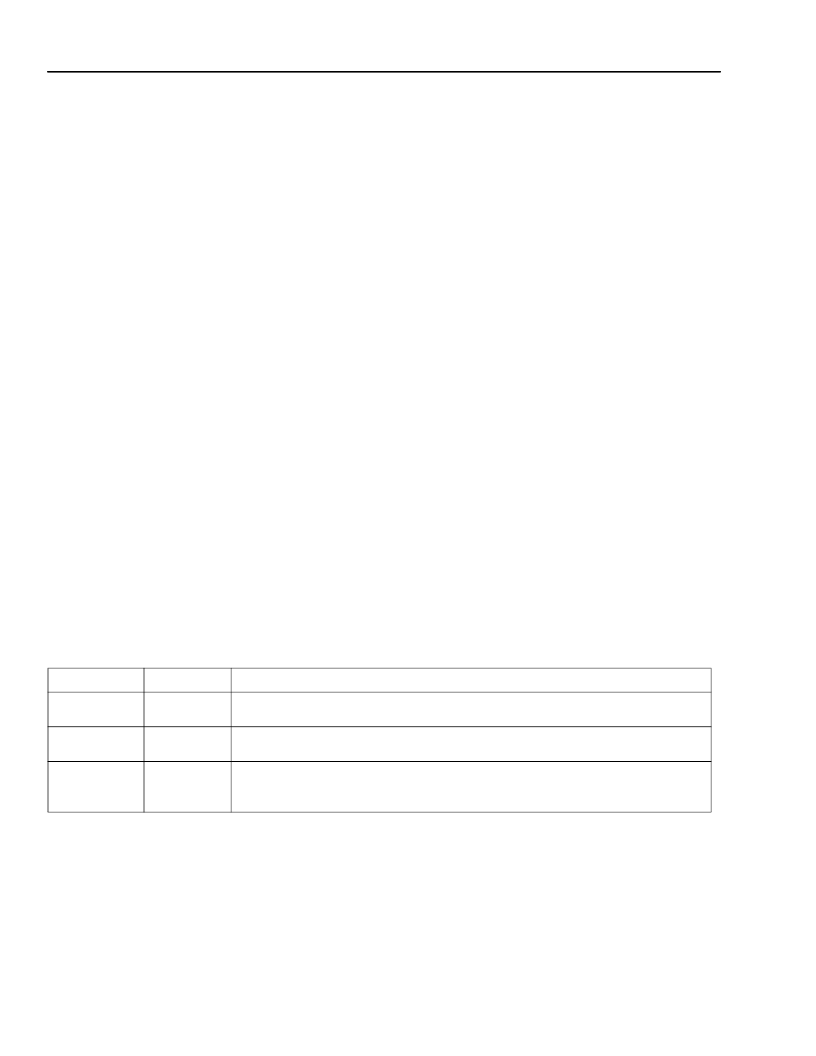

Table 44. Receiver Operation in Transparent Mode

Note:

The match bit (FMATCH) affects both the transmitter and the receiver. Care should be taken to correctly program both the transmit idle

character and the receive match character before setting FMATCH. If the transmit idle character is programmed to FF (hex), the FMATCH

bit appears to affect only the receiver.

FALOCT

X

FMATCH

0

Receiver Operation

Serial-to-parallel conversion begins with first RFDLCK after FRE, register

FDL_PR1 bit 2, is set. Data loaded to receive FIFO immediately.

Match user-defined character using sliding window. Byte aligns once character is

recognized. No data to receive FIFO until match is detected.

Match user-defined character, but only on octet boundary. Boundary based on

first RFDLCK after FRE, register FDL_PR1 bit 2, set. No data to receive FIFO

until match is detected.

0

1

1

1

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| TFRA08C13 | Ultraframer DS3/E3/DS2/E2/DS1/E1/DS0 |

| TFS380C | VI TELEFILTER Filter specification |

| TFT0675F | Anti-Aliasing and Reconstruction TFT range |

| TFT0675S | Anti-Aliasing and Reconstruction TFT range |

| TFT1350F | Anti-Aliasing and Reconstruction TFT range |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| TFRA08C13-DB | 制造商:AGERE 制造商全稱:AGERE 功能描述:TFRA08C13 OCTAL T1/E1 Framer |

| TFRA28J133BAL-1 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Telecomm/Datacomm |

| TFRA84J13 | 制造商:AGERE 制造商全稱:AGERE 功能描述:Ultraframer DS3/E3/DS2/E2/DS1/E1/DS0 |

| TFRA84J131BL-3-DB | 制造商:LSI Corporation 功能描述:Framer DS0/DS1/DS2/DS3/E1/E2/E3 1.5V/3.3V 909-Pin BGA |

| TFRA84J13DS0 | 制造商:AGERE 制造商全稱:AGERE 功能描述:Ultraframer DS3/E3/DS2/E2/DS1/E1/DS0 |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。