- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄98229 > THS8210PFP (TEXAS INSTRUMENTS INC) SPECIALTY CONSUMER CIRCUIT, PQFP80 PDF資料下載

參數(shù)資料

| 型號: | THS8210PFP |

| 廠商: | TEXAS INSTRUMENTS INC |

| 元件分類: | 消費(fèi)家電 |

| 英文描述: | SPECIALTY CONSUMER CIRCUIT, PQFP80 |

| 封裝: | POWER, PLASTIC, TQFP-80 |

| 文件頁數(shù): | 46/73頁 |

| 文件大小: | 2053K |

| 代理商: | THS8210PFP |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁當(dāng)前第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁

THS8200/8210

‘ALL-FORMAT’ OVERSAMPLED COMPONENT VIDEO/PC GRAPHICS D/A SYSTEM WITH

THREE 11 BIT DAC’S, CGMS DATA INSERTION AND 525P MACROVISION

TM COPY

PROTECTION

SLES032—6/18/02 3:33 PM

POST OFFICE BOX 655303 DALLAS TEXAS 77265

50

Copyright 2001 Texas Instruments Incorporated

PRODUCT PREVIEW information concerns products in the

formative or design phase of development. Characteristic data

and other specifications are design goals. Texas Instruments

reserves the right to change or discontinue these products

without notice.

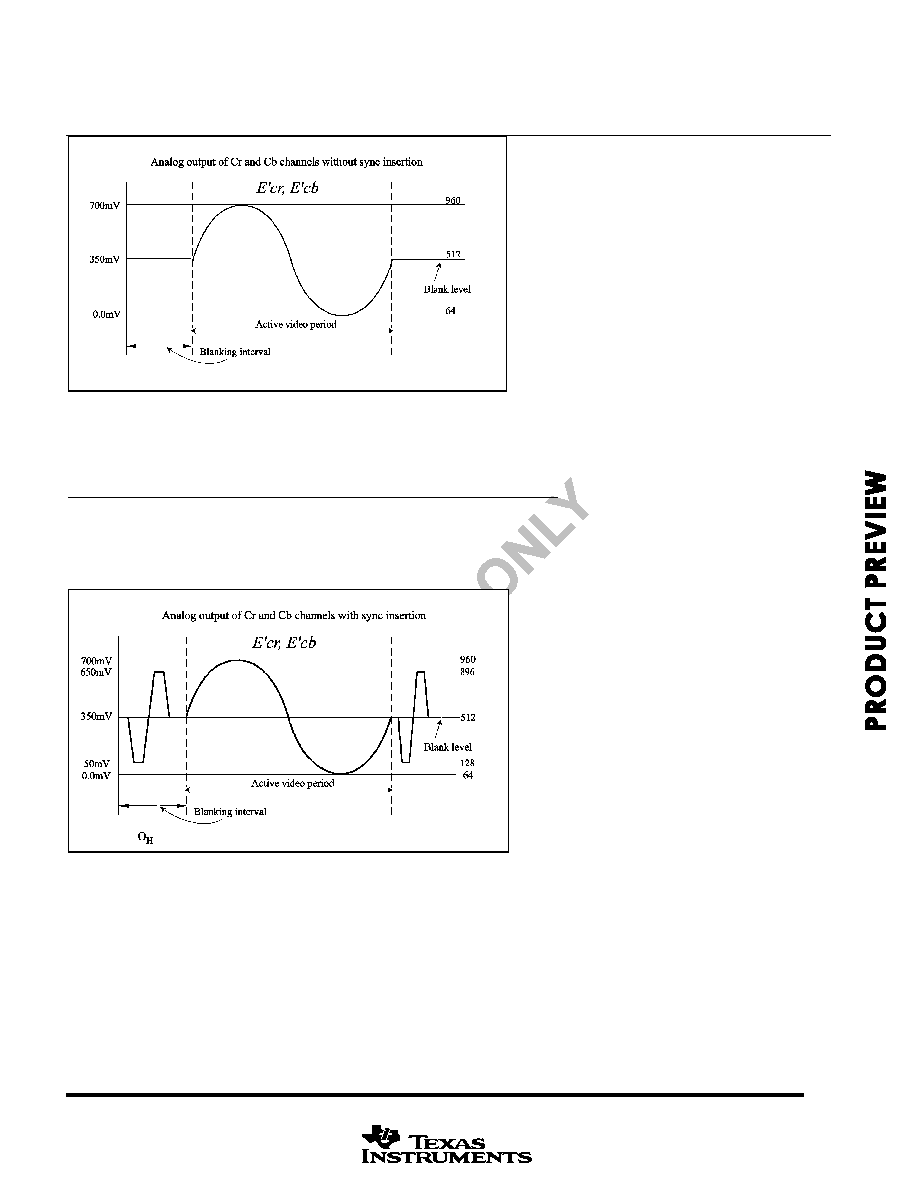

The blanking level of all channels is at 350mV. Note that for Pb and Pr output channels, there is no DC offset

added so DAC input code 0 now corresponds to 0V DC output. Whether or not offset is added to the DAC outputs

is determined from register setting ‘dtg2_rgb_mode_on’.

SMPTE compatible YPbPr output with sync signal inserted on all channels

In this mode, sync signals are inserted on all three channels Y, Cr and Cb. The Y channel output is identical to

before. The Pb,Pr channel outputs are shown below. The range of input code to Y channel is from 64 to 940. The

range of input code of CrCb channels is from 64 to 960.

The AC dynamic range during active video period is the same on all channels: 700 mV. But the corresponding

input code ranges are different. The input code range of Y is from 64 to 940; the input code range of Cr and Cb is

64 to 960. This means that two different code ranges are mapped to a same analog output range. Since three

DACs in THS8200 share a common full-scale adjust resistor, therefore, different input codes to the DAC will result

in different analog outputs. In order to map two code ranges into a same analog output, the input code range

should be scaled in the CSM block.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| TK10840MCBX | FM, AUDIO DEMODULATOR, PDSO20 |

| TK10840MCMG | FM, AUDIO DEMODULATOR, PDSO20 |

| TK10840MCTL | FM, AUDIO DEMODULATOR, PDSO20 |

| TK10840MCTR | FM, AUDIO DEMODULATOR, PDSO20 |

| TK10840MCTX | FM, AUDIO DEMODULATOR, PDSO20 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| THS8-38R-D | 制造商:Thomas & Betts 功能描述:HEAT SHRINK RING 8AWG 3/8 STUD 制造商:Thomas & Betts 功能描述:CATAMOUNT CABLE TIES |

| THS8-516R-D | 制造商:Thomas & Betts 功能描述:CATAMOUNT CABLE TIES |

| THS8-BS-W | 制造商:Thomas & Betts 功能描述:HEAT SHRINK BUTT SPLICE 8AWG |

| THS9 | 制造商:Apex Tool Group 功能描述:HS-9 9/32 HEX NUTDRIVER |

| THS9000 | 制造商:TI 制造商全稱:Texas Instruments 功能描述:50 MHz to 400 MHz CASCADEABLE AMPLIFIER |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。