- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄373714 > TS68230CFN8 (意法半導(dǎo)體) HMOS PARALLEL INTERFACE/TIMER PDF資料下載

參數(shù)資料

| 型號(hào): | TS68230CFN8 |

| 廠商: | 意法半導(dǎo)體 |

| 英文描述: | HMOS PARALLEL INTERFACE/TIMER |

| 中文描述: | HMO的并行接口/定時(shí)器 |

| 文件頁(yè)數(shù): | 36/61頁(yè) |

| 文件大小: | 2911K |

| 代理商: | TS68230CFN8 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)當(dāng)前第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)

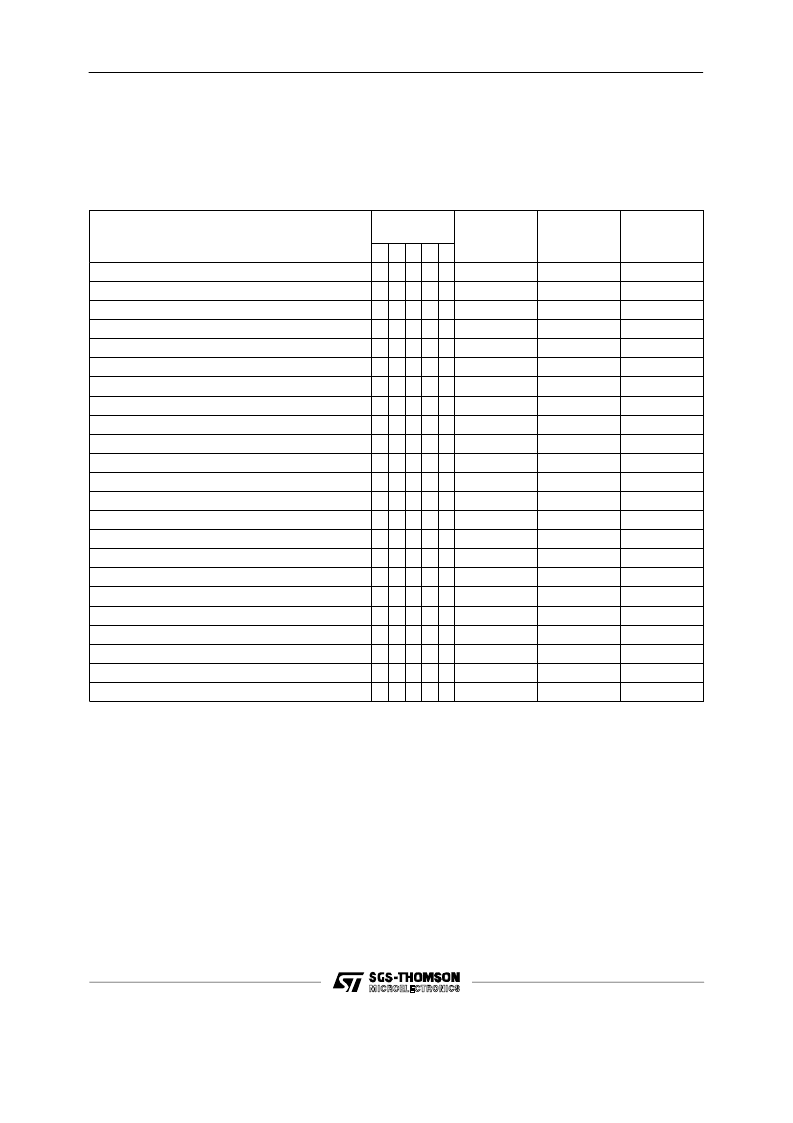

PROGRAMMER’S MODEL

This section describes the internal accessible regis-

ter organization as represented in table 1.3 located

at the end of this document and in table 4.1. Address

space within the address map is reserved for future

expansion.

Table 4.1 :

PI/T Register Addressing Assignments

.

Register

Select Bits

5 4 3 2 1

0 0 0 0 0

0 0 0 0 1

0 0 0 1 0

0 0 0 1 1

0 0 1 0 0

0 0 1 0 1

0 0 1 1 0

0 0 1 1 1

0 1 0 0 0

0 1 0 0 1

0 1 0 1 0

0 1 0 1 1

0 1 1 0 0

0 1 1 0 1

1 0 0 0 0

1 0 0 0 1

1 0 0 1 1

1 0 1 0 0

1 0 1 0 1

1 0 1 1 1

1 1 0 0 0

1 1 0 0 1

1 1 0 1 0

Register

Accessible

Affected by

Reset

Affected by

Read Cycle

Port General Control Register

Port Service Request Register

Port A Data Direction Register

Port B Data Direction Register

Port C Data Direction Register

Port Interrupt Vector Register

Port A Control Register

Port B Control Register

Port A Data Register

Port B Data Register

Port A Alternate Register

Port B Alternate Register

Port C Data Register

Port Status Register

Timer Control Register

Timer Interrupt Vector Register

Counter Preload Register High

Counter Preload Register Middle

Counter Preload Register Low

Count Register High

Count Register Middle

Count Register Low

Timer Status Register

(PGCR)

(PSRR)

(PADDR)

(PBDDR)

(PCDDR)

(PIVR)

(PACR)

(PBCR)

(PADR)

(PBDR)

(PAAR)

(PBAR)

(PCDR)

(PSR)

(TCR)

(TIVR)

(CPRH)

(CPRM)

(CPRL)

(CNTRH)

(CNTRM)

(CNTRL)

(TSR)

R W

R W

R W

R W

R W

R W

R W

R W

R W

R W

R

R

R W

R W*

R W

R W

R W

R W

R W

R

R

R

R W*

Yes

Yes

Yes

Yes

Yes

Yes

Yes

Yes

No

No

No

No

No

Yes

Yes

Yes

No

No

No

No

No

No

Yes

No

No

No

No

No

No

No

No

**

**

No

No

No

No

No

No

No

No

No

No

No

No

No

R = Read.

W = Write.

Throughout this section the following conventions

are maintained :

1. A read from a reserved location in the map re-

sults in a read from the "null register". The null

register returns all zeros for data and results in

a normal bus cycle. A write to one of these lo-

cations results in a normal bus cycle, but writ-

ten data is ignored.

2. Unused bits of a defined register are denoted

by "*" and are read as zeros ; written data is i-

gnored.

3. Bits that are unused in the chosen mode/sub-

mode but are used in others are denoted by

"X", and are readable and writable. Their

content, however, is ignored in the chosen

mode/submode.

4. All registers are addressable as 8-bit quanti-

ties. To facilitate operation with the MOVEP

instruction and the DMAC, addresses are or-

dered such that certain sets of registers may

also be accessed as words (two bytes) or long

words (four bytes).

SECTION 4

*

A write to this register may perform a special resetting opera-

TS68230

36/61

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| TS68302DESC01QYA | Integrated Multiprotocol Processor IMP |

| TS68302VA16 | Integrated Multiprotocol Processor IMP |

| TS68302 | Integrated Multiprotocol Processor IMP |

| TS68302MR16 | Integrated Multiprotocol Processor IMP |

| TS68302VR16 | Integrated Multiprotocol Processor IMP |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| TS68230CP10 | 制造商:STME 功能描述: |

| TS68230CP8 | 制造商:STMICROELECTRONICS 制造商全稱:STMicroelectronics 功能描述:HMOS PARALLEL INTERFACE/TIMER |

| TS68230FN | 制造商:STMICROELECTRONICS 制造商全稱:STMicroelectronics 功能描述:HMOS PARALLEL INTERFACE/TIMER |

| TS68230MC1B/C10 | 制造商:e2v technologies 功能描述: |

| TS68230MCB/C8 | 制造商:e2v technologies 功能描述: |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。