- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄373714 > TS68230CFN8 (意法半導(dǎo)體) HMOS PARALLEL INTERFACE/TIMER PDF資料下載

參數(shù)資料

| 型號(hào): | TS68230CFN8 |

| 廠商: | 意法半導(dǎo)體 |

| 英文描述: | HMOS PARALLEL INTERFACE/TIMER |

| 中文描述: | HMO的并行接口/定時(shí)器 |

| 文件頁數(shù): | 52/61頁 |

| 文件大小: | 2911K |

| 代理商: | TS68230CFN8 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁當(dāng)前第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁

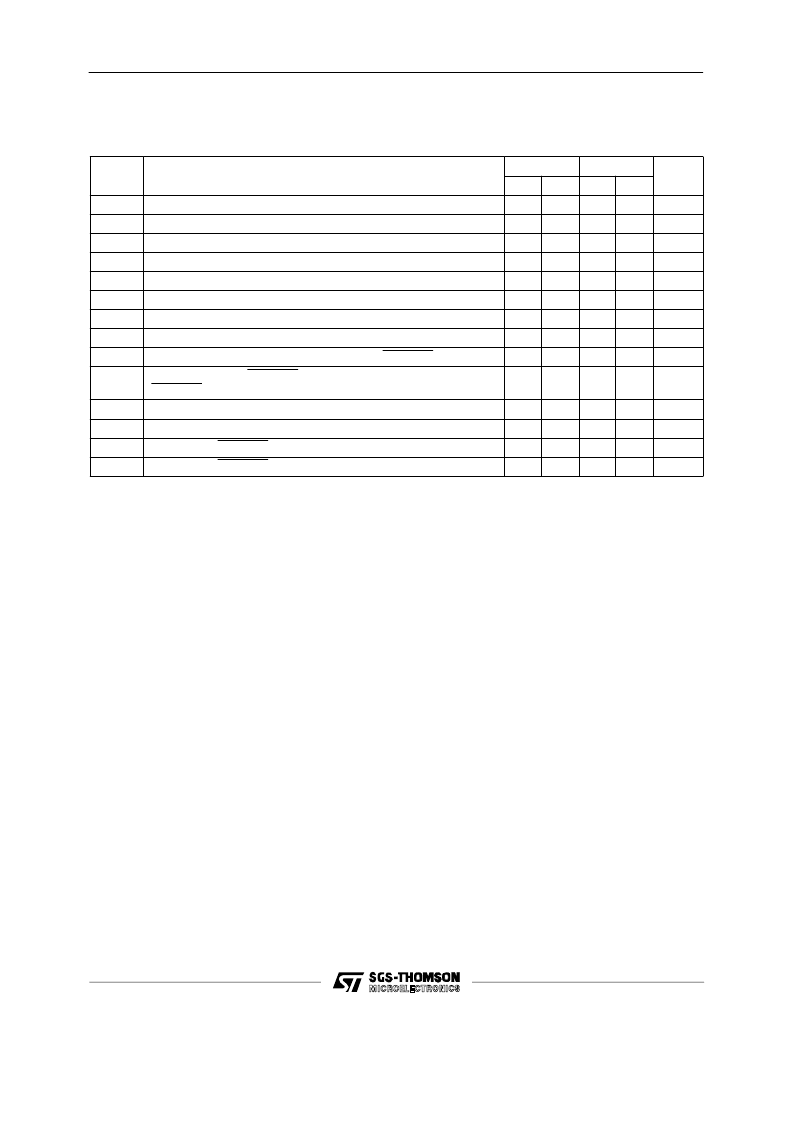

6.6. AC ELECTRICAL SPECIFICATIONS

(V

CC

= 5.0Vdc

±

5%, V

SS

= 0Vdc, T

A

= T

L

to T

H

unless otherwise noted)

Peripheral Input Timings

(figures 6.4)

8MHz

Min.

100

20

40

40

10MHz

Min.

60

20

40

40

Number

Parameter

Max.

Max.

Unit

14

15

16

17

18

19

20

(1)

21

(2)

22

(3.4)

23

Port Input Data Valid to H1(H3) Asserted (setup time)

H1(H3) Asserted to Port Input Data Invalid (hold time)

Handshake Input H1(H4) Pulse Width Asserted

Handshake Input H1(H4) Pulse Width Negated

H1(H3) Asserted to H2(H4) Negated (delay time)

CLK Low to H2(H4) Asserted (delay time)

H2(H4) Asserted to H1(H3) Asserted

CLK Low to H2(H4) Pulse Negated (delay time)

Synchronized H1(H3) to CLK low on which DMAREQ is asserted

CLK

low

on

which

DMAREQ

is

asserted

to

CLK

low

on which

DMAREQ is negated

H1(H3) Asserted to CLK High (setup time)

Synchronized H1(H3) to CLK low on which H2(H4) is asserted

CLK Low to DMAREQ Low (delay time)

CLK Low to DMAREQ High (delay time)

ns

ns

ns

ns

ns

ns

ns

ns

150

100

120

100

0

0

125

3.5

3

125

3.5

3

2.5

2.5

2.5

2.5

CLK Per

CLK Per

30

(5)

33

(3.4)

35

36

50

3.5

0

0

40

3.5

0

0

ns

4.5

120

120

4.5

100

100

CLK Per

ns

ns

If these two signals are derived from different sources they will have different instantaneous frequency variations. In

this case the frequency applied to the TIN pin must be distinctly less than the frequency at the CLK pin to avoid lost

cycles of the TIN signal. With signals derived from different crystal oscillators applied to the TIN and CLK pins with

fast rise and fall times, the TIN frequency can approach 80 to 90% of the frequency of the CLK signal without a loss

of a cycle of the TIN signal.

If these signals are derived from the same frequency source then the frequency of the signal applied to TIN can be

100% of the frequency at the CLK pin. They may be generated by different buffers from the same signal or one

may be an inverted version of the other. The TIN signal may be generated by an ’AND’ function of the clock and a

control signal.

TS68230

52/61

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| TS68302DESC01QYA | Integrated Multiprotocol Processor IMP |

| TS68302VA16 | Integrated Multiprotocol Processor IMP |

| TS68302 | Integrated Multiprotocol Processor IMP |

| TS68302MR16 | Integrated Multiprotocol Processor IMP |

| TS68302VR16 | Integrated Multiprotocol Processor IMP |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| TS68230CP10 | 制造商:STME 功能描述: |

| TS68230CP8 | 制造商:STMICROELECTRONICS 制造商全稱:STMicroelectronics 功能描述:HMOS PARALLEL INTERFACE/TIMER |

| TS68230FN | 制造商:STMICROELECTRONICS 制造商全稱:STMicroelectronics 功能描述:HMOS PARALLEL INTERFACE/TIMER |

| TS68230MC1B/C10 | 制造商:e2v technologies 功能描述: |

| TS68230MCB/C8 | 制造商:e2v technologies 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。