- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄361790 > W6692A TE Mode S/T Controller with PCI 2.2 Interface and ACPT PDF資料下載

參數(shù)資料

| 型號(hào): | W6692A |

| 英文描述: | TE Mode S/T Controller with PCI 2.2 Interface and ACPT |

| 中文描述: | TE模S / T的2.2與PCI控制器接口和ACPT |

| 文件頁數(shù): | 21/101頁 |

| 文件大小: | 851K |

| 代理商: | W6692A |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁當(dāng)前第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁

W6692A

Publication Release Date: July 2000

- 21 -

Revision A1

After hardware reset, the receiver may enter power down state in order to save power consumption.

In this state, the internal clocks are turned off, but the analog level detector is still active to detect

signal coming from the S interface. The power down state is left either by non-INFO 0 signal from S

interface or C/I command from microprocessor.

7.2.2 Receiver Clock Recovery And Timing Generation

A Digital Phase Locked Loop (DPLL) circuit is used to derive the receive clock from the received data

stream. This DPLL uses a 7.68 MHz clock as reference. According to I.430, the transmit clock is

normally delayed by 2 bit time from the receive clock. The "total phase deviation from input to output"

is -7% to +15% of a bit period. In some cases, delay compensation may be needed to meet this

requirement (see OPS1-0 bits in D_CTL register).

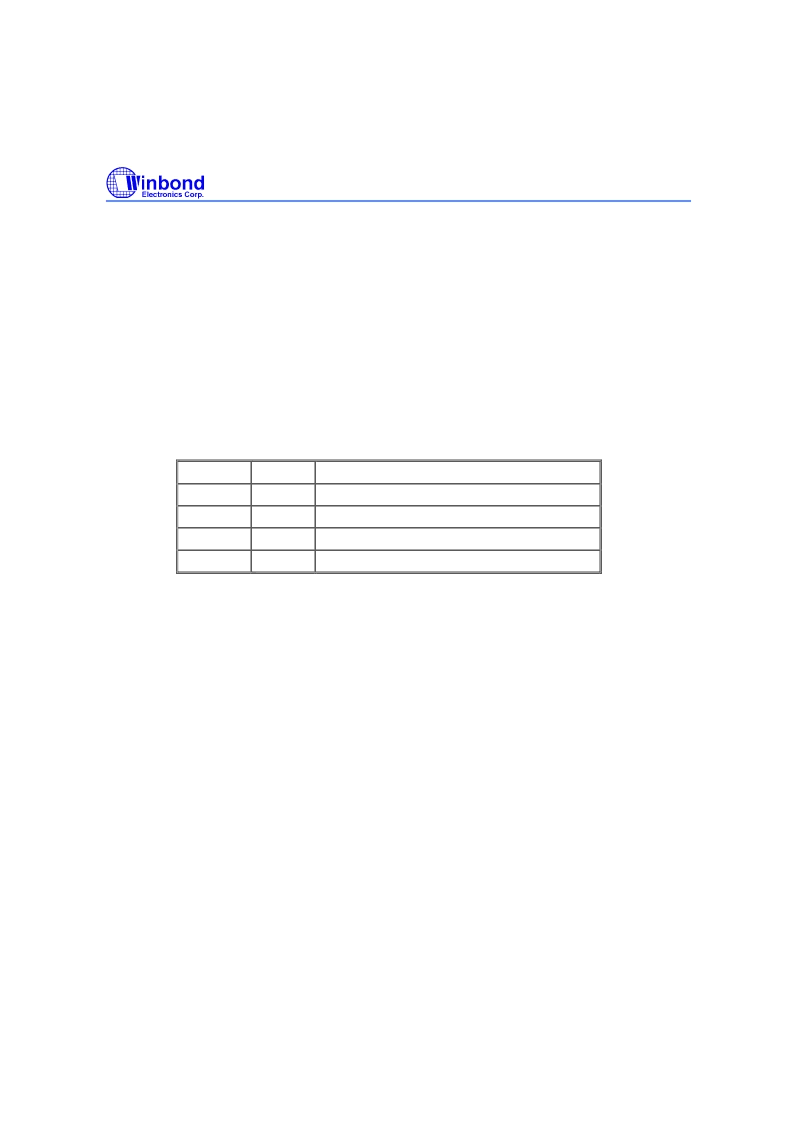

TABLE 7.1 OUTPUT PHASE DELAY COMPENSATION TABLE

OPS1

OPS0

Effect

0

0

No phase delay compensation

0

1

Phase delay compensation 260 nS

1

0

Phase delay compensation 520 nS

1

1

Phase delay compensation 1040 nS

W6692A does not need RC filter on receiver side, therefore zero delay compensation is selected

normally. This is also the default setting.

The PCM output clocks (PFCK1-2, PBCK) are locked to the S-interface timing with jitter. See the

electrical specification.

7.2.3 Layer 1 Activation/Deactivation

The layer 1 activation/deactivation procedures are implemented by a finite state machine according

to TE mode. The state transitions are triggered by signals received at S interface or commands

issued from microprocessor. The state outputs signals to S interface and indication to

microprocessor. The CIX register is used by microprocessor to issue command, and the CIR register

is used by microprocessor to receive indication.

Some commands are used for special purposes. They are "layer 1 reset", "analog loopback", "send

continuous zeros" and "send single zero".

7.2.3.1 States Descriptions And Command/Indication Codes

F3 Deactivated without clock

This is the "deactivated" state of ITU-T I.430. The receive line awake unit is active except during a

hardware reset pulse. After reset, once the indication "1111" has been read out, internal clocks will

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| W6692ACD | ISDN LINE INTERFACE|BASIC|CMOS|QFP|100PIN|PLASTIC |

| W6692ACF | ISDN LINE INTERFACE|BASIC|CMOS|QFP|100PIN|PLASTIC |

| W6694A | TE Mode S/T Controller with USB 1.1 Interface |

| W6694CD | USB Bus ISDN S/T-Controller |

| W7020 | Telecommunication IC |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| W6692ACD | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:ISDN LINE INTERFACE|BASIC|CMOS|QFP|100PIN|PLASTIC |

| W6692ACF | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:ISDN LINE INTERFACE|BASIC|CMOS|QFP|100PIN|PLASTIC |

| W6694 | 制造商:WINBOND 制造商全稱:Winbond 功能描述:USB Bus ISDN S/T-Controller |

| W6694A | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:TE Mode S/T Controller with USB 1.1 Interface |

| W6694CD | 制造商:WINBOND 制造商全稱:Winbond 功能描述:USB Bus ISDN S/T-Controller |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。