- 您現(xiàn)在的位置:買賣IC網 > PDF目錄4275 > XC2S200E-6FGG456C (Xilinx Inc)IC SPARTAN-IIE FPGA 200K 456FBGA PDF資料下載

參數(shù)資料

| 型號: | XC2S200E-6FGG456C |

| 廠商: | Xilinx Inc |

| 文件頁數(shù): | 12/108頁 |

| 文件大小: | 0K |

| 描述: | IC SPARTAN-IIE FPGA 200K 456FBGA |

| 標準包裝: | 60 |

| 系列: | Spartan®-IIE |

| LAB/CLB數(shù): | 1176 |

| 邏輯元件/單元數(shù): | 5292 |

| RAM 位總計: | 57344 |

| 輸入/輸出數(shù): | 289 |

| 門數(shù): | 200000 |

| 電源電壓: | 1.71 V ~ 1.89 V |

| 安裝類型: | 表面貼裝 |

| 工作溫度: | 0°C ~ 85°C |

| 封裝/外殼: | 456-BBGA |

| 供應商設備封裝: | 456-FBGA |

| 其它名稱: | 122-1323 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁當前第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁

DS077-2 (v3.0) August 9, 2013

11

Product Specification

Spartan-IIE FPGA Family: Functional Description

R

— OBSOLETE — OBSOLETE — OBSOLETE — OBSOLETE —

Optional pull-up and pull-down resistors and an optional

weak-keeper circuit are attached to each user I/O pad. Prior

to configuration all outputs not involved in configuration are

forced into their high-impedance state. The pull-down resis-

tors and the weak-keeper circuits are inactive, but inputs

may optionally be pulled up. The activation of pull-up resis-

tors prior to configuration is controlled on a global basis by

the configuration mode pins. If the pull-up resistors are not

activated, all the pins will float. Consequently, external

pull-up or pull-down resistors must be provided on pins

required to be at a well-defined logic level prior to configura-

tion.

All pads are protected against damage from electrostatic

discharge (ESD) and from over-voltage transients. After

configuration, clamping diodes are connected to VCCO for

LVTTL, PCI, HSTL, SSTL, CTT, and AGP standards.

All Spartan-IIE FPGA IOBs support IEEE 1149.1-compati-

ble boundary scan testing.

Input Path

A buffer in the IOB input path routes the input signal directly

to internal logic and through an optional input flip-flop.

An optional delay element at the D-input of this flip-flop elim-

inates pad-to-pad hold time. The delay is matched to the

internal clock-distribution delay of the FPGA, and when

used, assures that the pad-to-pad hold time is zero.

Each input buffer can be configured to conform to any of the

low-voltage signaling standards supported. In some of

these standards the input buffer utilizes a user-supplied

threshold voltage, VREF. The need to supply VREF imposes

constraints on which standards can used in close proximity

to each other. See I/O Banking.

There are optional pull-up and pull-down resistors at each

input for use after configuration.

Output Path

The output path includes a 3-state output buffer that drives

the output signal onto the pad. The output signal can be

routed to the buffer directly from the internal logic or through

an optional IOB output flip-flop.

The 3-state control of the output can also be routed directly

from the internal logic or through a flip-flip that provides syn-

chronous enable and disable.

Each output driver can be individually programmed for a

wide range of low-voltage signaling standards. Each output

buffer can source up to 24 mA and sink up to 48 mA. Drive

strength and slew rate controls minimize bus transients. The

default output driver is LVTTL with 12 mA drive strength and

slow slew rate.

In most signaling standards, the output high voltage

depends on an externally supplied VCCO voltage. The need

to supply VCCO imposes constraints on which standards

can be used in close proximity to each other. See I/O Bank-

ing.

An optional weak-keeper circuit is connected to each out-

put. When selected, the circuit monitors the voltage on the

pad and weakly drives the pin High or Low to match the

input signal. If the pin is connected to a multiple-source sig-

nal, the weak keeper holds the signal in its last state if all

drivers are disabled. Maintaining a valid logic level in this

way helps eliminate bus chatter.

Because the weak-keeper circuit uses the IOB input buffer

to monitor the input level, an appropriate VREF voltage must

be provided if the signaling standard requires one. The pro-

vision of this voltage must comply with the I/O banking

rules.

I/O Banking

Some of the I/O standards described above require VCCO

and/or VREF voltages. These voltages are externally sup-

plied and connected to device pins that serve groups of

IOBs, called banks. Consequently, restrictions exist about

which I/O standards can be combined within a given bank.

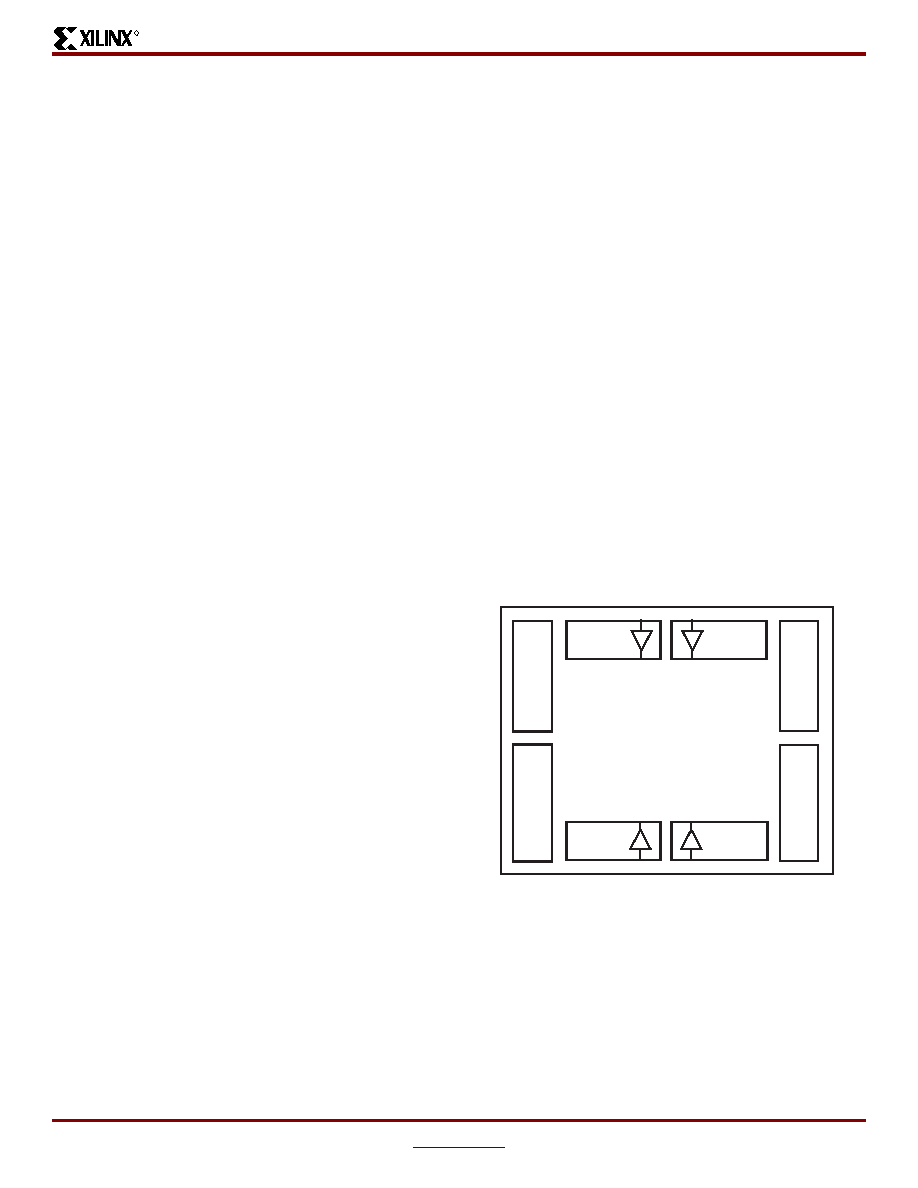

Eight I/O banks result from separating each edge of the

FPGA into two banks (see Figure 5). The pinout tables

show the bank affiliation of each I/O (see Pinout Tables,

connected to the same voltage. Voltage requirements are

determined by the output standards in use.

In the TQ144 and PQ208 packages, the eight banks have

VCCO connected together. Thus, only one VCCO level is

allowed in these packages, although different VREF values

are allowed in each of the eight banks.

Within a bank, standards may be mixed only if they use the

GTL and GTL+ appear under all voltages because their

open-drain outputs do not depend on VCCO. Note that VCCO

Figure 5: Spartan-IIE I/O Banks

DS077-2_02_051501

Bank 0

GCLK3

GCLK2

GCLK1

GCLK0

Bank 1

Bank 5

Bank 4

Spartan-IIE

Device

Bank

7

Bank

6

Bank

2

Bank

3

相關PDF資料 |

PDF描述 |

|---|---|

| XC2S200E-6FG456C | IC FPGA 1.8V 1176 CLB'S 456-FPGA |

| 93C86CT-E/SN | IC EEPROM 16KBIT 3MHZ 8SOIC |

| XA6SLX16-2FTG256Q | IC FPGA SPARTAN 6 256FTGBGA |

| GMC20DTEN | CONN EDGECARD 40POS .100 EYELET |

| 93C86C-E/SN | IC EEPROM 16KBIT 3MHZ 8SOIC |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| XC2S200E-6FGG456I | 制造商:XILINX 制造商全稱:XILINX 功能描述:Spartan-IIE FPGA |

| XC2S200E-6FGG676C | 制造商:XILINX 制造商全稱:XILINX 功能描述:Spartan-IIE FPGA |

| XC2S200E-6FGG676I | 制造商:XILINX 制造商全稱:XILINX 功能描述:Spartan-IIE FPGA |

| XC2S200E6FT256C | 制造商:Xilinx 功能描述: |

| XC2S200E-6FT256C | 制造商:XILINX 制造商全稱:XILINX 功能描述:Spartan-IIE 1.8V FPGA Family |

發(fā)布緊急采購,3分鐘左右您將得到回復。