- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄376464 > XRT91L82IB (EXAR CORP) 2.488/2.666 GBPS STS-48/STM-16 SONET/SDH TRANSCEIVER PDF資料下載

參數(shù)資料

| 型號: | XRT91L82IB |

| 廠商: | EXAR CORP |

| 元件分類: | 數(shù)字傳輸電路 |

| 英文描述: | 2.488/2.666 GBPS STS-48/STM-16 SONET/SDH TRANSCEIVER |

| 中文描述: | TRANSCEIVER, PBGA196 |

| 封裝: | 15 X 15 MM, STBGA-196 |

| 文件頁數(shù): | 12/59頁 |

| 文件大?。?/td> | 414K |

| 代理商: | XRT91L82IB |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁當(dāng)前第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁

XRT91L82

2.488/2.666 GBPS STS-48/STM-16 SONET/SDH TRANSCEIVER

PRELIMINARY

xr

REV. P1.0.5

9

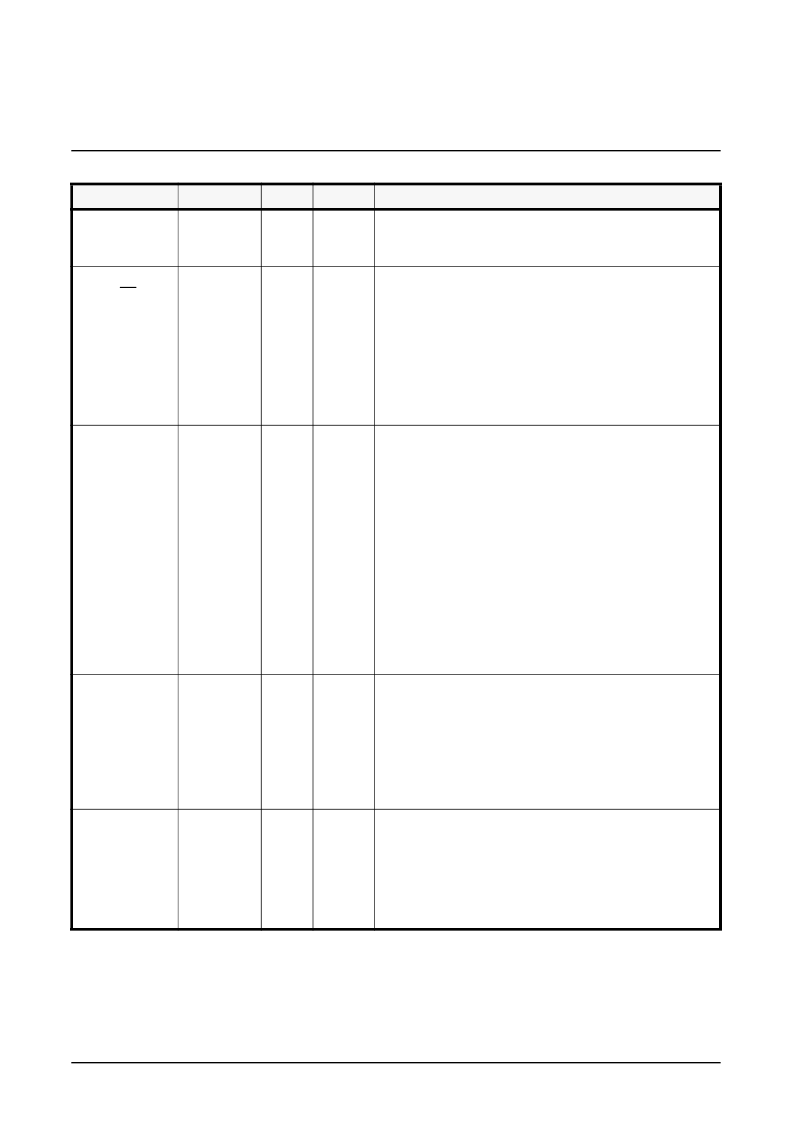

TXSCLKOP

TXSCLKON

CMLDIFF

O

A9

A8

2.488/2.666 GHz Transmit Serial Clock Output

A high-speed 2.488/2.666 GHz Transmit serial clock output that

can be used to retime TXOP/N.

TXSCLKOOFF

/ CS

LVTTL,

LVCMOS

I

C9

2.488/2.666 GHz Hi-speed Serial Clock Output Tristate

Hardware Mode

Tristates TXSCLKOP/N output and reduces

power consumption.

"Low" = TXSCLKOP/N output Enabled

"High" = Tristates TXSCLKOP/N output

This pin is provided with an internal pull-up.

Host Mode

This pin is functions as the microprocessor Chip

Select Input.

INTERM

/ VCXO_IN

LVTTL,

LVCMOS

/ SE-

LVCMOS

I

E4

Transmit Parallel Bus Input Internal Termination

Hardware Mode

Provides 100

line-to-line internal termina-

tion to TXDI[15:0]P/N and TXPCLKIP/N.

"Low" = Disabled

"High" = TXDI[15:0]P/N and TXPCLKIP/N internally terminated.

This pin is provided with an internal pull-down.

Host Mode - Voltage Controled 77.76/83.31 MHz or 155.52/

166.63 MHz External Oscillator Input

This 77.76/83.31 MHz or 155.52/166.63 MHz Single-Ended

LVCMOS clock input is used for the transmit PLL jitter attenua-

tion. ALTFREQSEL register bit determines the value used as

the reference. Software register bit VCXOSEL allows the selec-

tion of the De-Jitter VCXO Mode. See ALTFREQSEL and

VCXO_SEL software register bit description for more details.

TXPCLKIP

TXPCLKIN

LVDS,

LVPECL

Diff and SE

I

P11

P10

Transmit Parallel Clock Input

155.52 MHz clock input used to sample the 16-bit parallel trans-

mit data input TXDI[15:0]P/N. TXPCLKIP/N 100

internal ter-

mination is controlled by INTERM pin or register bit.

TXPCLKIP/N inputs are internally biased to VDD_IO - 1V for

AC coupled application.

N

OTE

:

The XRT91L82 can accept a 166.63 MHz transmit clock

input for Forward Error Correction (FEC) Applications.

TXPCLKOP

TXPCLKON

LVDS,

LVPECL

Diff and SE

O

P8

P7

Transmit Parallel Clock Output

This 155.52 MHz clock can be used for the downstream device

to generate the TXDI[15:0]P/N data and TXPCLKIP/N clock

input. This enables the downstream device and the STS-48

transceiver to be in synchronization.

N

OTE

:

The XRT91L82 can output a 166.63 MHz transmit clock

output for Forward Error Correction (FEC).

TRANSMITTER SECTION

N

AME

L

EVEL

T

YPE

P

IN

D

ESCRIPTION

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| XRT94L31_07 | 3-CHANNEL DS3/E3/STS-1 TO STS-3/STM-1 MAPPER IC |

| XRT94L31 | 3-CHANNEL DS3/E3/STS-1 TO STS-3/STM-1 MAPPER |

| XRT94L31IB | 3-CHANNEL DS3/E3/STS-1 TO STS-3/STM-1 MAPPER |

| XRT94L43A | SONET/SDH OC-12 TO 12XDS3/E3 MAPPER |

| XRT94L43 | SONET/SDH STS-12/STM-4 TO E3/DS3/STS-1 MAPPER/DEMAPPER |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| XRT91L82IB-F | 功能描述:總線收發(fā)器 Transceiver RoHS:否 制造商:Fairchild Semiconductor 邏輯類型:CMOS 邏輯系列:74VCX 每芯片的通道數(shù)量:16 輸入電平:CMOS 輸出電平:CMOS 輸出類型:3-State 高電平輸出電流:- 24 mA 低電平輸出電流:24 mA 傳播延遲時間:6.2 ns 電源電壓-最大:2.7 V, 3.6 V 電源電壓-最小:1.65 V, 2.3 V 最大工作溫度:+ 85 C 封裝 / 箱體:TSSOP-48 封裝:Reel |

| XRT94L31 | 制造商:EXAR 制造商全稱:EXAR 功能描述:3-CHANNEL DS3/E3/STS-1 TO STS-3/STM-1 MAPPER IC |

| XRT94L31_07 | 制造商:EXAR 制造商全稱:EXAR 功能描述:3-CHANNEL DS3/E3/STS-1 TO STS-3/STM-1 MAPPER IC |

| XRT94L31ES-L04 | 功能描述:時鐘合成器/抖動清除器 RoHS:否 制造商:Skyworks Solutions, Inc. 輸出端數(shù)量: 輸出電平: 最大輸出頻率: 輸入電平: 最大輸入頻率:6.1 GHz 電源電壓-最大:3.3 V 電源電壓-最小:2.7 V 封裝 / 箱體:TSSOP-28 封裝:Reel |

| XRT94L31IB | 功能描述:網(wǎng)絡(luò)控制器與處理器 IC Demapper RoHS:否 制造商:Micrel 產(chǎn)品:Controller Area Network (CAN) 收發(fā)器數(shù)量: 數(shù)據(jù)速率: 電源電流(最大值):595 mA 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:PBGA-400 封裝:Tray |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。