- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄373785 > ZL50018GAC (ZARLINK SEMICONDUCTOR INC) 2 K Digital Switch with Enhanced Stratum 3 DPLL PDF資料下載

參數(shù)資料

| 型號(hào): | ZL50018GAC |

| 廠商: | ZARLINK SEMICONDUCTOR INC |

| 元件分類: | 路由/交換 |

| 英文描述: | 2 K Digital Switch with Enhanced Stratum 3 DPLL |

| 中文描述: | TELECOM, DIGITAL TIME SWITCH, PBGA256 |

| 封裝: | 17 X 17 MM, 1.61 MM HEIGHT, PLASTIC, MS-034, BGA-256 |

| 文件頁(yè)數(shù): | 35/136頁(yè) |

| 文件大?。?/td> | 1448K |

| 代理商: | ZL50018GAC |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)當(dāng)前第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)第94頁(yè)第95頁(yè)第96頁(yè)第97頁(yè)第98頁(yè)第99頁(yè)第100頁(yè)第101頁(yè)第102頁(yè)第103頁(yè)第104頁(yè)第105頁(yè)第106頁(yè)第107頁(yè)第108頁(yè)第109頁(yè)第110頁(yè)第111頁(yè)第112頁(yè)第113頁(yè)第114頁(yè)第115頁(yè)第116頁(yè)第117頁(yè)第118頁(yè)第119頁(yè)第120頁(yè)第121頁(yè)第122頁(yè)第123頁(yè)第124頁(yè)第125頁(yè)第126頁(yè)第127頁(yè)第128頁(yè)第129頁(yè)第130頁(yè)第131頁(yè)第132頁(yè)第133頁(yè)第134頁(yè)第135頁(yè)第136頁(yè)

ZL50018

Data Sheet

35

Zarlink Semiconductor Inc.

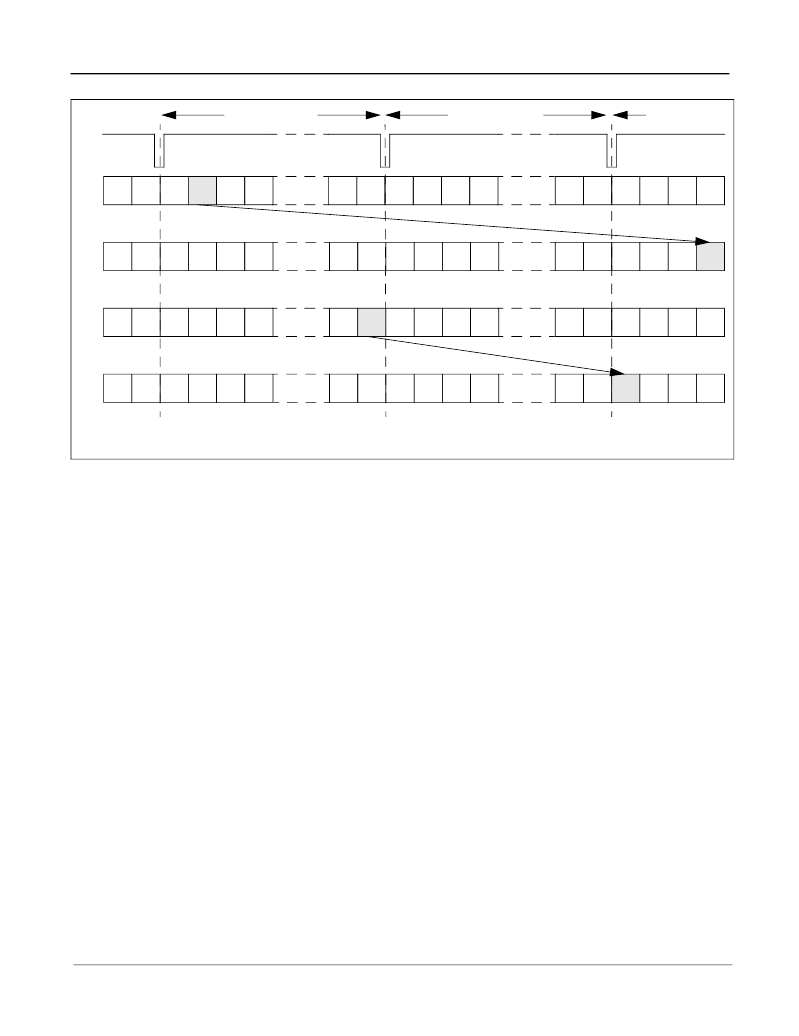

Figure 20 - Data Throughput Delay for Constant Delay

9.0 Connection Memory Description

The connection memory consists of two blocks, Connection Memory Low (CM_L) and Connection Memory High

(CM_H). The CM_L is 16 bits wide and is used for channel switching and other special modes. The CM_H is 5 bits

wide and is used for the voice coding function. When UAEN (bit 15) of the Connection Memory Low (CM_L) is low,

μ

-law/A-law conversion will be turned off and the contents of CM_H will be ignored. Each connection memory

location of the CM_L or CM_H can be read or written via the 16 bit microprocessor port within one microprocessor

access cycle. See Table 68 on page 100 for the address mapping of the connection memory. Any unused bits will

be reset to zero on the 16-bit data bus.

For the normal channel switching operation, CMM (bit 0) of the Connection Memory Low (CM_L) is programmed

low. SCA7 - 0 (bits 8 - 1) indicate the source (input) channel address and SSA4 - 0 (bits 13 - 9) indicate the source

(input) stream address. The 5-bit contents of the CM_H will be ignored during the normal channel switching mode

without the

μ

-law/A-law conversion when UAEN (bit 15) of the Connection Memory Low (CM_L) is set to zero. If

μ

-law/A-law conversion is required, the CM_H bits must be programmed first to provide the voice/data information,

the input coding law and the output coding law before the assertion of UAEN (bit 15) in the Connection Memory

Low.

When CMM (bit 0) of the Connection Memory Low (CM_L) is programmed high, the ZL50018 will operate in one of

the special modes described in Table 70 on page 102. When the per-channel message mode is enabled, MSG7 - 0

(bit 10 - 3) in the Connection Memory Low (CM_L) will be output via the serial data stream as message output data.

When the per-channel message mode is enabled, the

μ

-law/A-law conversion can also be enabled as required.

L-2 L-1 CH0CH1CH2CH3

L-2 L-1 CH0CH1CH2CH3

L-2 L-1 CH0CH1CH2CH3

L-2 L-1 CH0CH1CH2CH3

L-2 L-1 CH0CH1CH2CH3

L-2 L-1 CH0CH1CH2CH3

L-2 L-1 CH0CH1CH2CH3

L-2 L-1 CH0CH1CH2CH3

L-2 L-1 CH0CH1CH2CH3

L-2 L-1 CH0CH1CH2CH3

L-2 L-1 CH0CH1CH2CH3

L-2 L-1 CH0CH1CH2CH3

STi

STio

STi

STio

L = last channel = 31, 63, 127, or 255 for 2.048 Mbps, 4.096 Mbps, 8.192 Mbps, or 16.384 Mbps respectively.

Frame N

Frame N + 1

Frame N + 2

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ZL50018QCC | 2 K Digital Switch with Enhanced Stratum 3 DPLL |

| ZL50019 | Enhanced 2 K Digital Switch with Stratum 4E DPLL |

| ZL50019GAC | Enhanced 2 K Digital Switch with Stratum 4E DPLL |

| ZL50019QCC | Enhanced 2 K Digital Switch with Stratum 4E DPLL |

| ZL50022 | Enhanced 4 K Digital Switch with Stratum 4E DPLL |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ZL50018GAG2 | 制造商:Microsemi Corporation 功能描述:SWIT FABRIC 2K X 2K 1.8V/3.3V 256BGA - Trays 制造商:MICROSEMI CONSUMER MEDICAL PRODUCT GROUP 功能描述:IC TDM SWITCH 2K-CH ENH 256PBGA 制造商:Microsemi Corporation 功能描述:IC TDM SWITCH 2K-CH ENH 256PBGA |

| ZL50018QCC | 制造商:Microsemi Corporation 功能描述:SWIT FABRIC 2K X 2K 1.8V/3.3V 256LQFP - Trays |

| ZL50018QCG1 | 制造商:Microsemi Corporation 功能描述:PB FREE 2K+ RATE CONVERSION AND S3 DPLL - Trays 制造商:MICROSEMI CONSUMER MEDICAL PRODUCT GROUP 功能描述:IC TDM SWITCH 2K-CH ENH 256LQFP |

| ZL50019 | 制造商:ZARLINK 制造商全稱:Zarlink Semiconductor Inc 功能描述:Enhanced 2 K Digital Switch with Stratum 4E DPLL |

| ZL50019_06 | 制造商:ZARLINK 制造商全稱:Zarlink Semiconductor Inc 功能描述:Enhanced 2 K Digital Switch with Stratum 4E DPLL |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。