- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄378286 > ADV7330 (Analog Devices, Inc.) Multiformat 11-Bit Triple DAC Video Encoder PDF資料下載

參數(shù)資料

| 型號: | ADV7330 |

| 廠商: | Analog Devices, Inc. |

| 英文描述: | Multiformat 11-Bit Triple DAC Video Encoder |

| 中文描述: | 多格式11位DAC的視頻編碼器三 |

| 文件頁數(shù): | 6/76頁 |

| 文件大小: | 1378K |

| 代理商: | ADV7330 |

第1頁第2頁第3頁第4頁第5頁當前第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁

REV. B

–6–

ADV7330

TIMING SPECIFICATIONS

(V

AA

= 2.375 V to 2.625 V, V

= 2.375 V to 2.625 V; V

DD_IO

= 2.375 V to 3.6 V, V

= 1.235 V,

R

SET

= 3040

, R

LOAD

= 300 . All specifications T

MIN

MAX

(0 C to 70 C), unless otherwise noted.)

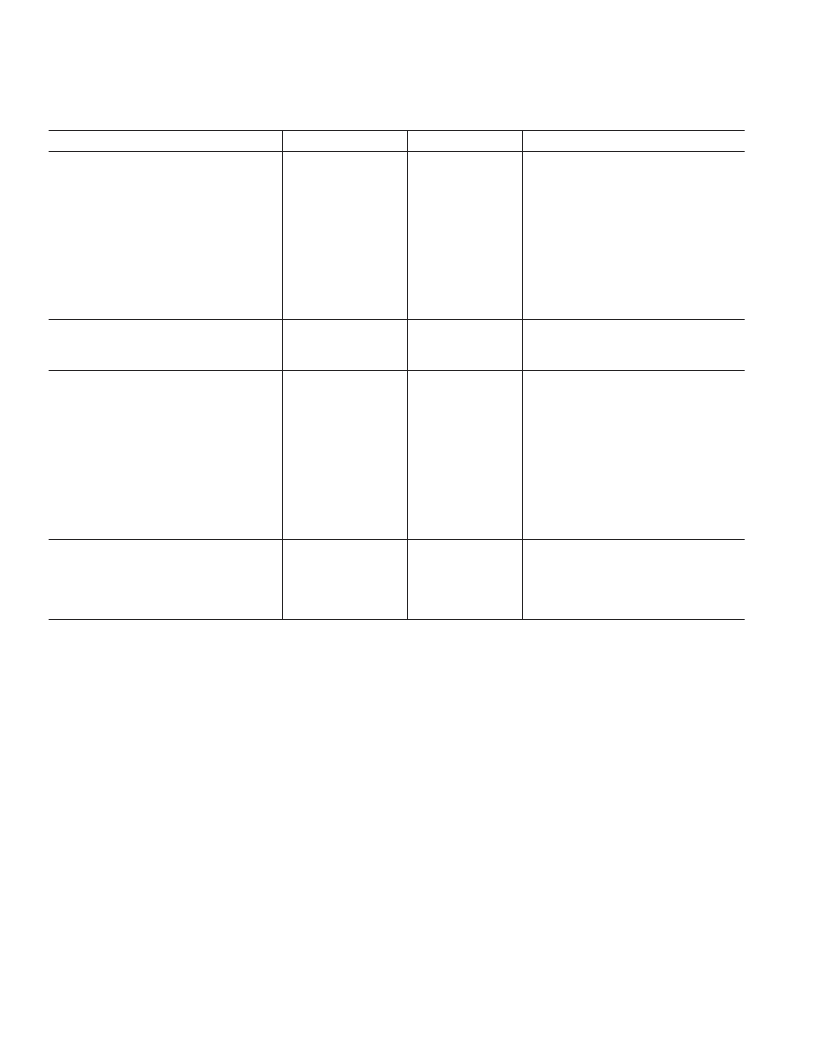

Parameter

MPU PORT

1

SCLOCK Frequency

SCLOCK High Pulsewidth, t

1

SCLOCK Low Pulsewidth, t

2

Hold Time (Start Condition), t

3

Setup Time (Start Condition), t

4

Data Setup Time, t

5

SDATA, SCLOCK Rise Time, t

6

SDATA, SCLOCK Fall Time, t

7

Setup Time (Stop Condition), t

8

RESET Low Time

Min

Typ

Max

Unit

Conditions

0

0.6

1.3

0.6

0.6

100

400

kHz

μ

s

μ

s

μ

s

μ

s

ns

ns

ns

μ

s

ns

After this period, the first clock is generated

Relevant for repeated start condition

300

300

0.6

100

ANALOG OUTPUTS

Analog Output Delay

2

Output Skew

CLOCK CONTROL AND PIXEL PORT

3

f

CLK

f

CLK

Clock High Time, t

9

Clock Low Time, t

10

Data Setup Time, t

111

Data Hold Time, t

121

SD Output Access Time, t

13

SD Output Hold Time, t

14

HD Output Access Time, t

13

HD Output Hold Time, t

14

PIPELINE DELAY

4

7

1

ns

ns

27

MHz

MHz

% of one clk cycle

% of one clk cycle

ns

ns

ns

ns

ns

ns

Progressive scan mode

HDTV mode/async mode

81

40

40

2.0

2.0

15

5.0

14

5.0

63

76

35

41

36

clk cycles

clk cycles

clk cycles

clk cycles

clk cycles

SD (2

×

, 16

×

)

SD component mode (16

×

)

PS (1

×

)

PS (8

×

)

HD (2

×

, 1

×

)

NOTES

1

Guaranteed by characterization.

2

Output delay measured from the 50% point of the rising edge of CLOCK to the 50% point of the DAC output full-scale transition.

3

Data: C [9:0]; Y [9:0], S[9:0].

Control:

HSYNC_I/P

,

VSYNC_I/P

,

BLANK_I/P

,

HSYNC_O/P

,

VSYNC_O/P

,

BLANK_O/P

.

4

SD, PS = 27 MHz, HD = 74.25 MHz.

Specifications subject to change without notice.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ADV7330KST | Multiformat 11-Bit Triple DAC Video Encoder |

| ADXL321 | Small and Thin 18 g Accelerometer |

| ADXL321EB | Small and Thin 18 g Accelerometer |

| ADXL321JCP | Small and Thin 18 g Accelerometer |

| ADXL321JCP-REEL | Small and Thin 18 g Accelerometer |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ADV73305502 | 制造商:LG Corporation 功能描述:FRAME ASSEMBLY |

| ADV73306701 | 制造商:LG Corporation 功能描述:Frame Assembly |

| ADV73306702 | 制造商:LG Corporation 功能描述:Frame Assembly |

| ADV73306703 | 制造商:LG Corporation 功能描述:Frame Assembly |

| ADV73306704 | 制造商:LG Corporation 功能描述:Frame Assembly |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。