- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄366550 > AM79C970AKC (ADVANCED MICRO DEVICES INC) PCnet-PCI II Single-Chip Full-Duplex Ethernet Controller for PCI Local Bus Product PDF資料下載

參數(shù)資料

| 型號(hào): | AM79C970AKC |

| 廠商: | ADVANCED MICRO DEVICES INC |

| 元件分類(lèi): | 微控制器/微處理器 |

| 英文描述: | PCnet-PCI II Single-Chip Full-Duplex Ethernet Controller for PCI Local Bus Product |

| 中文描述: | 2 CHANNEL(S), 10M bps, LOCAL AREA NETWORK CONTROLLER, PQFP13 |

| 封裝: | CARRIER RING, PLASTIC, QFP-132 |

| 文件頁(yè)數(shù): | 89/219頁(yè) |

| 文件大?。?/td> | 1065K |

| 代理商: | AM79C970AKC |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)當(dāng)前第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)第94頁(yè)第95頁(yè)第96頁(yè)第97頁(yè)第98頁(yè)第99頁(yè)第100頁(yè)第101頁(yè)第102頁(yè)第103頁(yè)第104頁(yè)第105頁(yè)第106頁(yè)第107頁(yè)第108頁(yè)第109頁(yè)第110頁(yè)第111頁(yè)第112頁(yè)第113頁(yè)第114頁(yè)第115頁(yè)第116頁(yè)第117頁(yè)第118頁(yè)第119頁(yè)第120頁(yè)第121頁(yè)第122頁(yè)第123頁(yè)第124頁(yè)第125頁(yè)第126頁(yè)第127頁(yè)第128頁(yè)第129頁(yè)第130頁(yè)第131頁(yè)第132頁(yè)第133頁(yè)第134頁(yè)第135頁(yè)第136頁(yè)第137頁(yè)第138頁(yè)第139頁(yè)第140頁(yè)第141頁(yè)第142頁(yè)第143頁(yè)第144頁(yè)第145頁(yè)第146頁(yè)第147頁(yè)第148頁(yè)第149頁(yè)第150頁(yè)第151頁(yè)第152頁(yè)第153頁(yè)第154頁(yè)第155頁(yè)第156頁(yè)第157頁(yè)第158頁(yè)第159頁(yè)第160頁(yè)第161頁(yè)第162頁(yè)第163頁(yè)第164頁(yè)第165頁(yè)第166頁(yè)第167頁(yè)第168頁(yè)第169頁(yè)第170頁(yè)第171頁(yè)第172頁(yè)第173頁(yè)第174頁(yè)第175頁(yè)第176頁(yè)第177頁(yè)第178頁(yè)第179頁(yè)第180頁(yè)第181頁(yè)第182頁(yè)第183頁(yè)第184頁(yè)第185頁(yè)第186頁(yè)第187頁(yè)第188頁(yè)第189頁(yè)第190頁(yè)第191頁(yè)第192頁(yè)第193頁(yè)第194頁(yè)第195頁(yè)第196頁(yè)第197頁(yè)第198頁(yè)第199頁(yè)第200頁(yè)第201頁(yè)第202頁(yè)第203頁(yè)第204頁(yè)第205頁(yè)第206頁(yè)第207頁(yè)第208頁(yè)第209頁(yè)第210頁(yè)第211頁(yè)第212頁(yè)第213頁(yè)第214頁(yè)第215頁(yè)第216頁(yè)第217頁(yè)第218頁(yè)第219頁(yè)

P R E L I M I N A R Y

AMD

89

Am79C970A

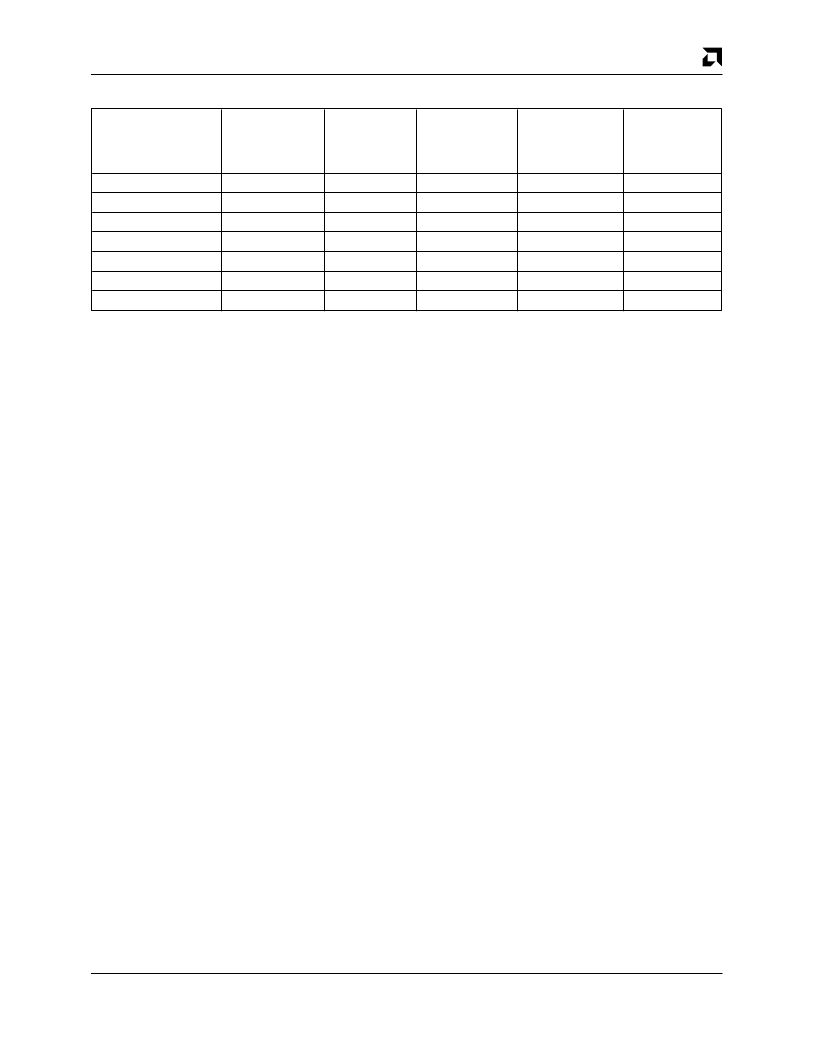

Table 10. GPSI Pin Configuration

PCnet-PCI II

Controller

Expansion

ROM Pin

PCnet-PCI II

Controller

GPSI Pin

PCnet-PCI II

Controller

Pin Number

C-LANCE

GPSI Pin

GPSI Function

GPSI I/O Type

Collision

I

CLSN

CLSN

81

ERD3

Receive Clock

I

RCLK

RXCLK

85

ERD1

Receive Data

I

RX

RXDAT

86

ERD0

Receive Enable

I

RENA

RXEN

83

ERD2

Transmit Clock

I

TCLK

TXCLK

80

ERD4

Transmit Data

O

TX

TXDAT

75

ERD7

Transmit Enable

O

TENA

TXEN

77

ERD6

Note that the XTAL1 input must always be driven with a

clock source, even if GPSI mode is to be used. It is not

necessary for the XTAL1 clock to meet the normal fre-

quency and stability requirements in this case. Any fre-

quency between 8 MHz and 20 MHz is acceptable.

However, voltage drive requirements do not change.

When GPSI mode is used, XTAL1 must be driven for

several reasons:

I

The default H_RESET configuration for the PCnet-

PCI II controller is AUI port selected and until GPSI

mode is selected, the XTAL1 clock is needed for

some internal operations (namely, RESET).

I

The XTAL1 clock drives the EEPROM read opera-

tion, regardless of the network mode selected.

I

The XTAL1 clock determines the length the internal

S_RESET caused by the read of the Reset register,

regardless of the network mode.

Note that if a clock slower than 20 MHz is provided at the

XTAL1 input, the time needed for EEPROM read and

the internal S_RESET will increase.

External Address Detection Interface

The External Address Detection Interface (EADI) is pro-

vided to allow external address filtering. It is selected by

setting the EADISEL bit in BCR2 to ONE. This feature is

typically utilized for terminal servers, bridges and/or

router products. The EADI interface can be used in con-

junction with external logic to capture the packet desti-

nation address from the serial bit stream as it arrives at

the PCnet-PCI II controller, compare the captured ad-

dress with a table of stored addresses or identifiers, and

then determine whether or not the PCnet-PCI II control-

ler should accept the packet.

The EADI interface outputs are delivered directly from

the NRZ decoded data and clock recovered by the

Manchester decoder or input into the GPSI port. This al-

lows the external address detection to be performed in

parallel with frame reception and address comparison in

the MAC Station Address Detection (SAD) block of the

PCnet-PCI II controller.

SRDCLK is provided to allow clocking of the receive bit

stream into the external address detection logic. Note

that when the 10BASE-T port is selected, transitions on

SRDCLK will only occur during receive activity. When

the AUI or GPSI port is selected, transitions on SRDCLK

will occur during both transmit and receive activity. Once

a received frame commences and data and clock are

available from the decoder, the EADI logic will monitor

the alternating (1,0) preamble pattern until the two

ONEs of the Start Frame Delimiter (SFD, 10101011 bit

pattern) are detected, at which point the SFBD output

will be driven HIGH.

The SFBD signal will initially be LOW. The assertion of

SFBD is a signal to the external address detection logic

that the SFD has been detected and that subsequent

SRDCLK cycles will deliver packet data to the external

logic. Therefore, when SFBD is asserted, the external

address matching logic should begin de-serialization of

the SRD data and send the resulting destination ad-

dress to a Content Addressable Memory (CAM) or other

address detection device. In order to reduce the amount

of logic external to the PCnet-PCI II controller for multi-

ple address decoding systems, the SFBD signal will

toggle at each new byte boundary within the packet,

subsequent to the SFD. This eliminates the need for ex-

ternally supplying byte framing logic.

SRD is the decoded NRZ data from the network. This

signal can be used for external address detection. Note

that when the 10BASE-T port is selected, transitions on

SRD will only occur during receive activity. When the

AUI or GPSI port is selected, transitions on SRD will oc-

cur during both transmit and receive activity.

The

EAR

pin should be driven LOW by the external ad-

dress comparison logic to reject a frame.

If an address match is detected by comparison with

either the Physical Address or Logical Address Filter

registers contained within the PCnet-PCI II controller or

the frame is of the type “Broadcast”, then the frame will

be accepted regardless of the condition of

EAR

. When

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| AM79C970A | PCnet-PCI II Single-Chip Full-Duplex Ethernet Controller for PCI Local Bus Product |

| AM79C970AVCW | PCnet-PCI II Single-Chip Full-Duplex Ethernet Controller for PCI Local Bus Product |

| AM79C970 | PCnetTM-PCI Single-Chip Ethernet Controller for PCI Local Bus |

| AM79C971VCW | PCnet⑩-FAST Single-Chip Full-Duplex 10/100 Mbps Ethernet Controller for PCI Local Bus |

| AM79C971 | PCnet⑩-FAST Single-Chip Full-Duplex 10/100 Mbps Ethernet Controller for PCI Local Bus |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| AM79C970AKC\\W | 制造商:Rochester Electronics LLC 功能描述:- Bulk 制造商:Advanced Micro Devices 功能描述: |

| AM79C970AKC\W | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| AM79C970AKCW | 制造商:AMD 制造商全稱(chēng):Advanced Micro Devices 功能描述:PCnet-PCI II Single-Chip Full-Duplex Ethernet Controller for PCI Local Bus Product |

| AM79C970AVC | 制造商:Advanced Micro Devices 功能描述: |

| AM79C970AVC\\W | 制造商:Advanced Micro Devices 功能描述: 制造商:Rochester Electronics LLC 功能描述: |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。