- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄370740 > HY5R256HC -|2.5V|8K|40|Direct RDRAM - 256M PDF資料下載

參數(shù)資料

| 型號: | HY5R256HC |

| 英文描述: | -|2.5V|8K|40|Direct RDRAM - 256M |

| 中文描述: | - |為2.5V | 8K的| 40 |直接RDRAM的- 256M |

| 文件頁數(shù): | 41/64頁 |

| 文件大?。?/td> | 4542K |

| 代理商: | HY5R256HC |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁當(dāng)前第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁

Rev.0.9 / Dec.2000

41

Direct RDRAM

256/288-Mbit (512Kx16/18x32s) Preliminary

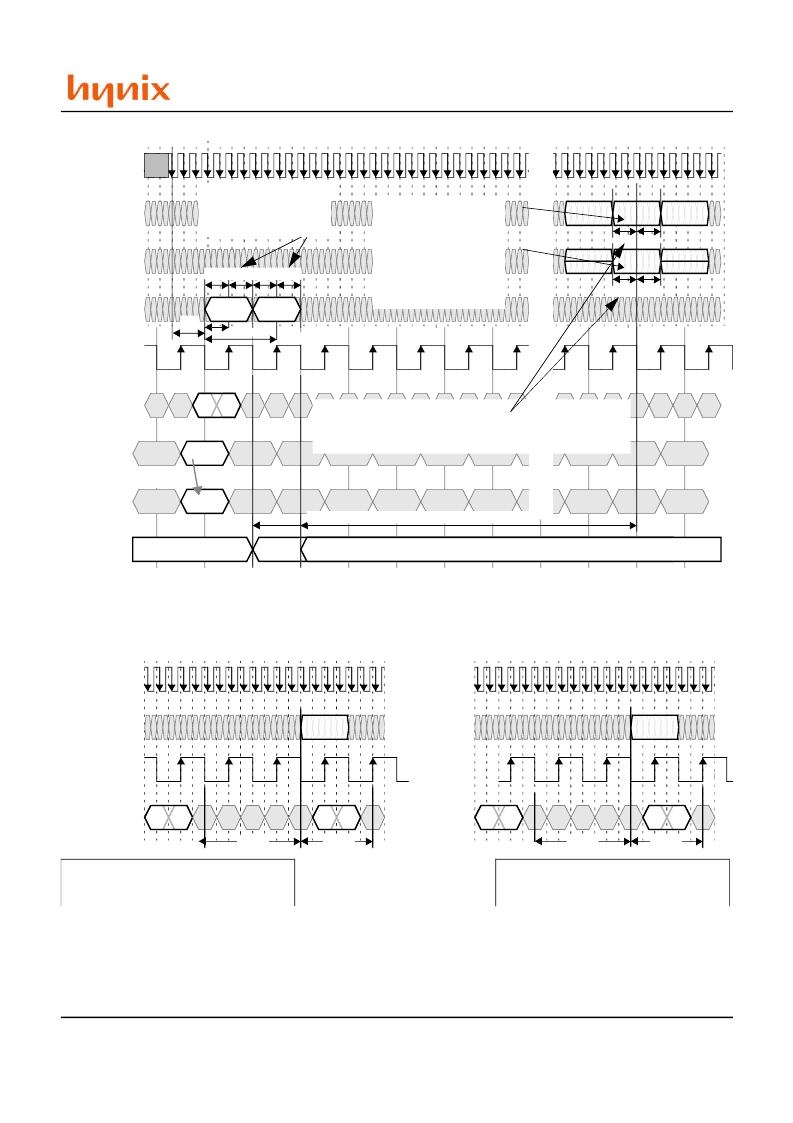

Figure 48: NAP and PDN Exit

Figure 49: NAP Entry/Exit Windows (left) and PDN Entry/Exit Windows (right)

CTM/CFM

DQA8..0

DQB8..0

COL4

..COL0

ROW2

..ROW0

T

0

T

4

T

8

T

12

T

1

T

5

T

9

T

13

T

2

T

6

T

10

T

14

T

3

T

7

T

11

T

15

T

16

T

20

T

24

T

28

T

17

T

21

T

25

T

29

T

18

T

22

T

26

T

30

T

19

T

23

T

27

T

31

T

32

T

36

T

40

T

44

T

33

T

37

T

41

T

45

T

34

T

38

T

42

T

46

T

35

T

39

T

43

T

47

ROP

DQS=0

b,c

SCK

CMD

SIO0

SIO1

0

1

0/1

a

0/1

a

PDEV5..0

b

PDEV5..0

b

DQS=1

b

t

S3

t

S3

t

H3

t

H3

t

CE

a

Use 0 for NAP exit, 1 for PDN exit

b

Device selection timing slot is selected by DQS field of NAPX register

The packet is repeated

from SIO0 to SIO1

restricted

Power

State

DQS=0

d

DQS=1

d

c

The DOS field must be written with “1” for this RDRAM

d

The PSX field determines the start of NAP / PDN exit.

t

S4

t

H4

restricted

STBY

NAP/PDN

(

NAPX)t

SCYCLE

)/(

256PDNXt

SCYCLE

)

t

S4

t

H4

COP

XOP

No ROW packets may

overlap the restricted interval

No COL packets may

overlap the restricted interval

if device PDEV is exiting the

NAP-A or PDN-A states

ROP

COP

XOP

If PSX = 1 in Init register,

then NAP / PDN exit is

broadcast (no PDEV field)

Effective hold becomes

t

H4

’=t

H4

+ [PDNXA *64* t

SCYCLE

+ t

PDNXB,MAX

]-[PDNX*256*t

SCYCLE]

if [PDNX*256*t

SCYCLE

] < [PDNXA *64* t

SCYCLE

+ t

PDNXB,MAX

]

CTM/CFM

CMD

SCK

ROW2

..ROW0

T

0

T

4

T

8

T

12

T

1

T

5

T

9

T

13

T

2

T

6

T

10

T

14

T

3

T

7

T

11

T

15

T

16

T

20

T

17

T

21

T

18

T

22

T

19

T

23

NAPR

CTM/CFM

CMD

SCK

ROW2

..ROW0

T

0

T

4

T

8

T

12

T

1

T

5

T

9

T

13

T

2

T

6

T

10

T

14

T

3

T

7

T

11

T

15

T

16

T

20

T

17

T

21

T

18

T

19

0

1

0

1

t

NU0

no entry

t

NU0

= 5t

CYCLE

+ (2+NAPX)t

SCYCLE

t

NU1

= 8t

CYCLE

- (0.5t

SCYCLE

)

= 23t

CYCLE

PDNR

0

1

0

1

no exit

t

NU1

t

PU0

no entry

no exit

t

PU1

if NSR=1

if NSR=0

t

PU0

= 5t

CYCLE

+ (2+256PDNX)t

SCYCLE

t

PU1

= 8t

CYCLE

- (0.5t

SCYCLE

)

= 23t

CYCLE

if PSR=1

if PSR=0

NAP entry

NAP exit

PDN entry

PDN exit

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| HY5R288HC | -|2.5V|8K|40|Direct RDRAM - 288M |

| HY5V16CF | 1Mx16|3.3V|4K|H|SDR SDRAM - 16M |

| HY5V16CF-H | x16 SDRAM |

| HY5V16CF-S | x16 SDRAM |

| HY6116-10 | x8 SRAM |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| HY5S2B6DLF-BE | 制造商:HYNIX 制造商全稱:Hynix Semiconductor 功能描述:4Banks x 2M x 16bits Synchronous DRAM |

| HY5S2B6DLFP-BE | 制造商:HYNIX 制造商全稱:Hynix Semiconductor 功能描述:4Banks x 2M x 16bits Synchronous DRAM |

| HY5S2B6DLFP-SE | 制造商:HYNIX 制造商全稱:Hynix Semiconductor 功能描述:4Banks x 2M x 16bits Synchronous DRAM |

| HY5S2B6DLF-SE | 制造商:HYNIX 制造商全稱:Hynix Semiconductor 功能描述:4Banks x 2M x 16bits Synchronous DRAM |

| HY5S5B2BLF-6E | 制造商:HYNIX 制造商全稱:Hynix Semiconductor 功能描述:256M (8Mx32bit) Mobile SDRAM |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。