- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄2002 > ISLA214S50IR1Z (Intersil)IC ADC PDF資料下載

參數(shù)資料

| 型號: | ISLA214S50IR1Z |

| 廠商: | Intersil |

| 文件頁數(shù): | 19/41頁 |

| 文件大小: | 0K |

| 描述: | IC ADC |

| 標(biāo)準(zhǔn)包裝: | 1 |

| 系列: | * |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁當(dāng)前第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁

ISLA214S50

26

FN7973.2

April 25, 2013

Serial Peripheral Interface

A serial peripheral interface (SPI) bus is used to facilitate

configuration of the device and to optimize performance. The SPI

bus consists of chip select (CSB), serial clock (SCLK) serial data

output (SDO), and serial data input/output (SDIO). The maximum

SCLK rate is equal to the ADC sample rate (fSAMPLE) divided by 14

for write operations and fSAMPLE divided by 32 for reads. There is

no minimum SCLK rate.

The following sections describe various registers that are used to

configure the SPI or adjust performance or functional parameters.

Many registers in the available address space (0x00 to 0xFF) are

not defined in this document. Additionally, within a defined

register there may be certain bits or bit combinations that are

reserved. Undefined registers and undefined values within defined

registers are reserved and should not be selected. Setting any

reserved register or value may produce indeterminate results.

SPI Physical Interface

The serial clock pin (SCLK) provides synchronization for the data

transfer. By default, all data is presented on the serial data

input/output (SDIO) pin in three-wire mode. The state of the SDIO

pin is set automatically in the communication protocol

(described in the following). A dedicated serial data output pin

(SDO) can be activated by setting 0x00[7] high to allow operation

in four-wire mode.

The SPI port operates in a half duplex master/slave

configuration, with the ADC functioning as a slave. Multiple slave

devices can interface to a single master in three-wire mode only,

since the SDO output of an unaddressed device is asserted in

four wire mode.

The chip-select bar (CSB) pin determines when a slave device is

being addressed. Multiple slave devices can be written to

concurrently, but only one slave device can be read from at a

given time (again, only in three-wire mode). If multiple slave

devices are selected for reading at the same time, the results will

be indeterminate.

The communication protocol begins with an instruction/address

phase. The first rising SCLK edge following a high-to-low

transition on CSB determines the beginning of the two-byte

instruction/address command; SCLK must be static low before

the CSB transition. Data can be presented in MSB-first order or

LSB-first order. The default is MSB-first, but this can be changed

bit ordering for the MSB-first and LSB-first modes, respectively. In

MSB-first mode, the address is incremented for multi-byte

transfers, while in LSB-first mode it’s decremented.

In the default mode, the MSB is R/W, which determines if the

data is to be read (active high) or written. The next two bits, W1

and W0, determine the number of data bytes to be read or

written (see Table 6). The lower 13 bits contain the first address

for the data transfer. This relationship is illustrated in Figure 44,

and timing values are given in “Switching Specifications” on

After the instruction/address bytes have been read, the

appropriate number of data bytes are written to or read from the

ADC (based on the R/W bit status). The data transfer will

continue as long as CSB remains low and SCLK is active. Stalling

of the CSB pin is allowed at any byte boundary

(instruction/address or data) if the number of bytes being

transferred is three or less. For transfers of four bytes or more,

CSB is allowed to stall in the middle of the instruction/address

bytes or before the first data byte. If CSB transitions to a high

state after that point the state machine will reset and terminate

the data transfer.

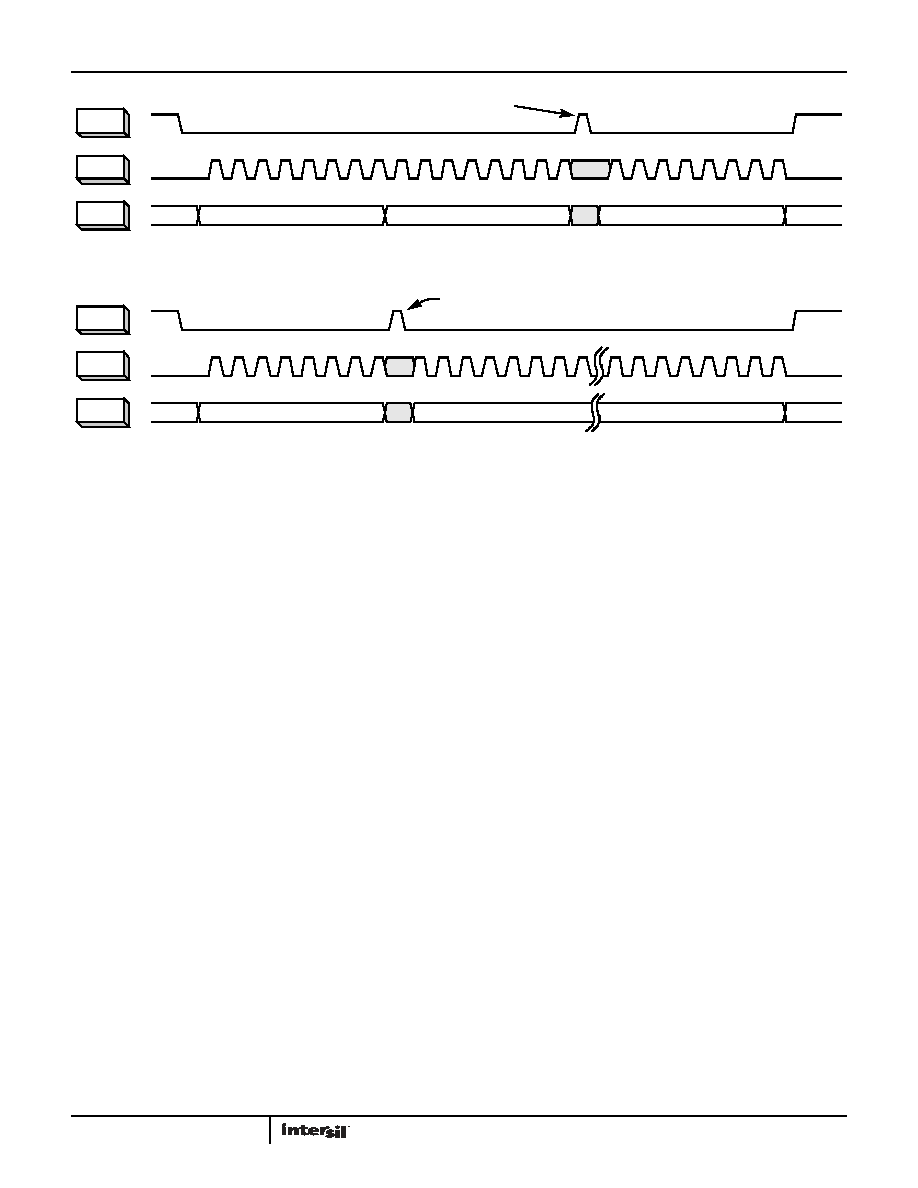

FIGURE 46. 2-BYTE TRANSFER

CSB

SCLK

SDIO

INSTRUCTION/ADDRESS

DATA WORD 1

DATA WORD 2

CSB STALLING

FIGURE 47. N-BYTE TRANSFER

CSB

SCLK

SDIO

INSTRUCTION/ADDRESS

DATA WORD 1

DATA WORD N

LAST LEGAL

CSB STALLING

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ISLA222P13IRZ | IC ADC 12BIT SRL/SPI 72QFN |

| ISLA224S25IR1Z | IC ADC |

| KAD2708C-27Q68 | IC ADC 8BIT 275MSPS PAR 68-QFN |

| KAD2708L-27Q68 | IC ADC 8BIT 275MSPS PAR 68-QFN |

| KAD2710C-27Q68 | IC ADC 10BIT 275MSPS PAR 68-QFN |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ISLA214S50IR48EV1Z | 制造商:Intersil Corporation 功能描述:ISLA214S50IRZ EVALUATION BOARD 1 48LD QFN ROHS COMPLIANT - Bulk 制造商:Intersil Corporation 功能描述:ISLA214S50IRZ EVALUATION BOARD 1 48LD QFN ROHS COMPLIANT |

| ISLA216IR72EV1Z | 制造商:Intersil Corporation 功能描述:ISLA216IR72 EVAL BOARD - 72 LD QFN - SINGLE 16-BIT 250MSPS U - Bulk 制造商:Intersil Corporation 功能描述:EVAL BOARD FOR ISLA216IR72 制造商:Intersil Corporation 功能描述:EVAL BOARD ADC ISLA216P 制造商:Intersil Corporation 功能描述:EVAL BOARD, ADC, ISLA216P 制造商:Intersil 功能描述:ISLA216IR72 EVALRD 72LD SNGL 16-BIT 制造商:Intersil Corporation 功能描述:EVAL BOARD, ADC, ISLA216P; Silicon Manufacturer:Intersil; Silicon Core Number:ISLA216P; Kit Application Type:Data Converter; Application Sub Type:ADC; Kit Contents:Evaluation Board for ISLA216P ADC |

| ISLA216P | 制造商:INTERSIL 制造商全稱:Intersil Corporation 功能描述:16-Bit, 250MSPS/200MSPS/130MSPS ADC |

| ISLA216P_1104 | 制造商:INTERSIL 制造商全稱:Intersil Corporation 功能描述:16-Bit, 250MSPS/200MSPS/130MSPS ADC |

| ISLA216P13 | 制造商:INTERSIL 制造商全稱:Intersil Corporation 功能描述:12-Bit, 500MSPS ADC Programmable Built-in Test Patterns |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。