- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄67723 > ISP1583ET2 (NXP SEMICONDUCTORS) UNIVERSAL SERIAL BUS CONTROLLER, PBGA64 PDF資料下載

參數(shù)資料

| 型號: | ISP1583ET2 |

| 廠商: | NXP SEMICONDUCTORS |

| 元件分類: | 總線控制器 |

| 英文描述: | UNIVERSAL SERIAL BUS CONTROLLER, PBGA64 |

| 封裝: | 6 X 6 MM, 0.80 MM HEIGHT, LEAD FREE, PLASTIC, MO-195, SOT543-1,TFBGA-64 |

| 文件頁數(shù): | 80/100頁 |

| 文件大?。?/td> | 508K |

| 代理商: | ISP1583ET2 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁當(dāng)前第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁

ISP1583_7

NXP B.V. 2008. All rights reserved.

Product data sheet

Rev. 07 — 22 September 2008

79 of 99

NXP Semiconductors

ISP1583

Hi-Speed USB peripheral controller

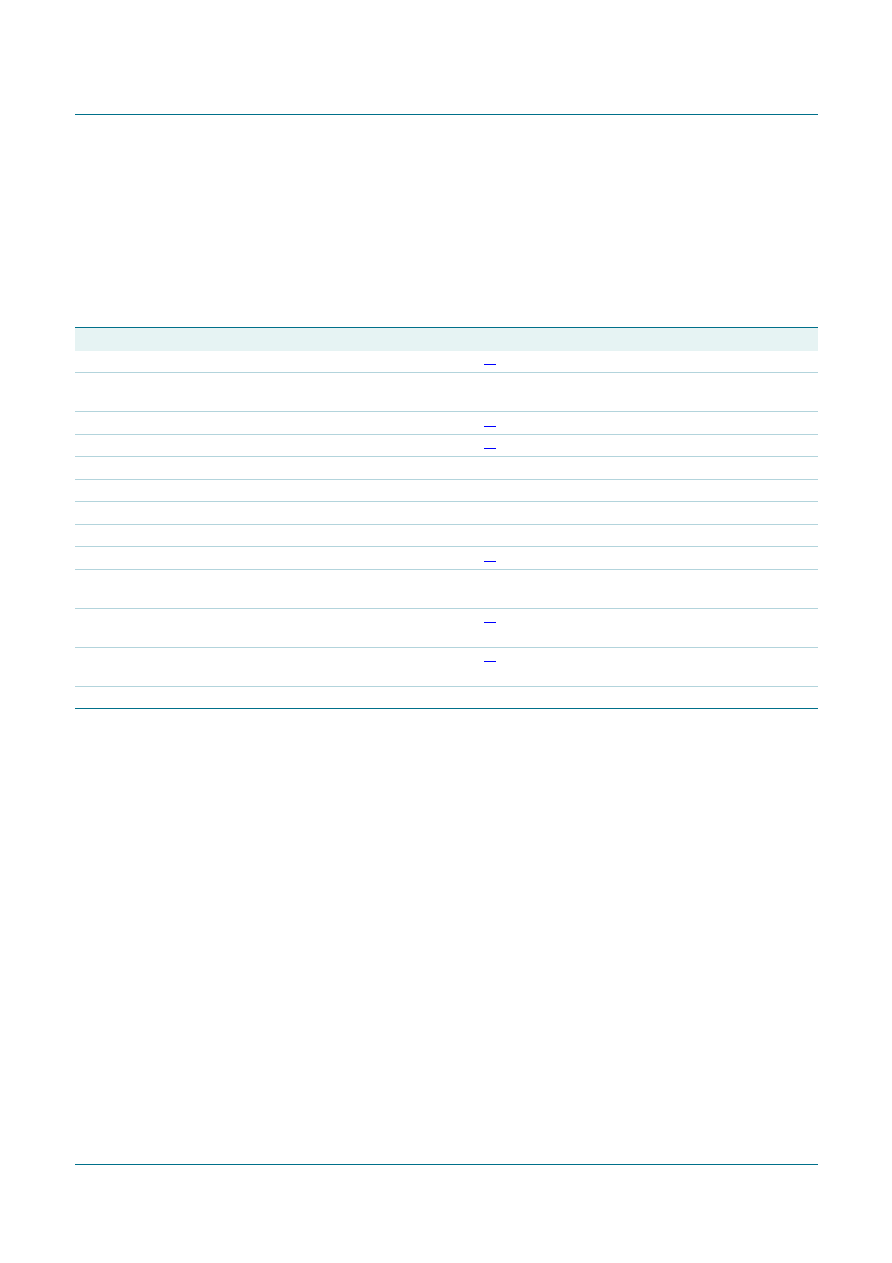

13.2 DMA timing

13.2.1 PIO mode

Remark: In the following subsections, RW_N/RD_N, DS_N/WR_N, READY/IORDY and

ALE/A0 refer to the ISP1583 pin.

[1]

Tcy1 is the total cycle time, consisting of command active time tw1 and command recovery (inactive) time tw2, that is, Tcy1 = tw1 + tw2.

Minimum timing requirements for Tcy1, tw1 and tw2 must all be met. As Tcy1(min) is greater than the sum of tw1(min) and tw2(min), a host

implementation must lengthen tw1 and/or tw2 to ensure that Tcy1 is equal to or greater than the value reported in the IDENTIFY DEVICE

data. A device implementation shall support any legal host implementation.

[2]

td2 species the time after DIOR is negated, when the data bus is no longer driven by the device (3-state).

[3]

If READY/IORDY is LOW at tsu4, the host waits until READY/IORDY is made HIGH before the PIO cycle is completed. In that case, tsu5

must be met for reading (tsu3 does not apply). When READY/IORDY is HIGH at tsu4, tsu3 must be met for reading (tsu5 does not apply).

Table 108. PIO mode timing parameters

VCC(I/O) = 1.65 V to 3.6 V; VCC(3V3) = 3.3 V; VGND = 0 V; Tamb = 40 °C to +85 °C; unless otherwise specied.

Symbol Parameter

Conditions

Mode 0 Mode 1 Mode 2 Mode 3 Mode 4 Unit

Tcy1(min) read or write cycle time

[1] 600

383

240

180

120

ns

tsu1(min)

address to DIOR or DIOW on set-up

time

70

50

30

25

ns

tw1(min)

DIOR or DIOW pulse width

[1] 165

125

100

80

70

ns

tw2(min)

DIOR/DIOW recovery time

[1] ---70

25

ns

tsu2(min)

data set-up time before DIOW off

60

45

30

20

ns

th2(min)

data hold time after DIOW off

30

20

15

10

ns

tsu3(min)

data set-up time before DIOR on

50

35

20

ns

th3(min)

data hold time after DIOR off

5

ns

td2(max)

data to 3-state delay after DIOR off

[2] 30

30

ns

th1(min)

address hold time after DIOR or DIOW

off

20

15

10

ns

tsu4(min)

READY/IORDY after DIOR or DIOW on

set-up time

[3] 35

35

ns

tsu5(min)

read data to READY/IORDY HIGH

set-up time

[3] 00000ns

tw3(max)

READY/IORDY LOW pulse width

1250

ns

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ISP1761ET,518 | UNIVERSAL SERIAL BUS CONTROLLER, PBGA128 |

| ISP1761BE,518 | UNIVERSAL SERIAL BUS CONTROLLER, PQFP128 |

| ISP1761BE,551 | UNIVERSAL SERIAL BUS CONTROLLER, PQFP128 |

| ISP1761BE,518 | UNIVERSAL SERIAL BUS CONTROLLER, PQFP128 |

| ITR8307 | SPECIALTY OPTOELECTRONIC DEVICE |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ISP1583ET2,518 | 功能描述:外圍驅(qū)動器與原件 - PCI USB 2.0 DEVICE RoHS:否 制造商:PLX Technology 工作電源電壓: 最大工作溫度: 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FCBGA-1156 封裝:Tray |

| ISP1583ET2-T | 功能描述:外圍驅(qū)動器與原件 - PCI USB 2.0 DEVICE RoHS:否 制造商:PLX Technology 工作電源電壓: 最大工作溫度: 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FCBGA-1156 封裝:Tray |

| ISP1583ET-T | 功能描述:外圍驅(qū)動器與原件 - PCI HI-SPEED USB2 DEVICE RoHS:否 制造商:PLX Technology 工作電源電壓: 最大工作溫度: 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FCBGA-1156 封裝:Tray |

| ISP1583ETUM | 功能描述:IC USB CTRL HI-SPEED 64TFBGA RoHS:是 類別:集成電路 (IC) >> 接口 - 控制器 系列:- 標(biāo)準(zhǔn)包裝:4,900 系列:- 控制器類型:USB 2.0 控制器 接口:串行 電源電壓:3 V ~ 3.6 V 電流 - 電源:135mA 工作溫度:0°C ~ 70°C 安裝類型:表面貼裝 封裝/外殼:36-VFQFN 裸露焊盤 供應(yīng)商設(shè)備封裝:36-QFN(6x6) 包裝:* 其它名稱:Q6396337A |

| ISP166 | 功能描述:機(jī)架和機(jī)柜配件 PANELS 1600HX600D RoHS:否 制造商:Bivar 產(chǎn)品:Rack Accessories 面板空間: 顏色:Black |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。