- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄359155 > MCZ33742EG (飛思卡爾半導體(中國)有限公司) System Basis Chip (SBC) with Enhanced High-Speed CAN Transceiver PDF資料下載

參數(shù)資料

| 型號: | MCZ33742EG |

| 廠商: | 飛思卡爾半導體(中國)有限公司 |

| 元件分類: | CAN |

| 英文描述: | System Basis Chip (SBC) with Enhanced High-Speed CAN Transceiver |

| 中文描述: | 系統(tǒng)基礎芯片的增強型(SBC)的高速CAN收發(fā)器 |

| 文件頁數(shù): | 25/65頁 |

| 文件大小: | 1158K |

| 代理商: | MCZ33742EG |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁當前第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁

Analog Integrated Circuit Device Data

Freescale Semiconductor

25

33742

FUNCTIONAL DEVICE OPERATION

OPERATIONAL MODES

NORMAL MODE

In Normal mode, both the

VDD

and V2 regulators are in the

ON state. All functions are available in this operating mode

(watchdog, wake-up input reading through SPI, HS

activation, and CAN communication). The watchdog timer is

running and must be periodically cleared through SPI.

STOP MODE

The V2 regulator is turned OFF by disabling the V2CTRL

pin. The VDD regulator is activated in a special low power

mode supplying only a few mA of current. This maintains

“keep alive” power for the application’s MCU while the MCU

is in a power-saving state (i.e., a MCU’s version of Stop or

Wait). In the Stop mode, the supply current available from

VSUP

pin is very low.

Both parts (the SBC or the MCU) can be awakened from

either the 33742 side (for example, cyclic sense, forced

wake-up, CAN message, wake-up inputs, and overcurrent on

VDD) or from the MCU side (key wake-up, etc.).

Stop mode

is always selected via SPI. In Stop mode, the

watchdog software may be either running or not running

depending upon selection by SPI (Reset Control Register

[RCR], bit WDSTOP). To clear a running watchdog timer, the

SBC must be awakened using the CS pin (SPI wake-up). In

Stop mode, wake-up is identical to that in Sleep mode, with

the addition of CS and VDD overcurrent wake-up. Refer to

Table 7

, page

25

.

SLEEP MODE

In Sleep mode, the VDD

and V2 regulators are OFF.

Current consumption from the VSUP pin is cut. In Sleep

mode, the SBC can be awakened by sensing individual level

individual level changes in the L0 L3 inputs, by cyclic

checking of the L0 L3 inputs, by the forced wake-up timer, or

from the CAN physical interface upon receiving a CAN

message. When a wake-up occurs, the SBC goes first into

the Reset mode

before entering Normal Request mode.

RESET MODE

In the Reset mode, the RST pin is LOW and a timer runs

for t

RSTDUR

time. After t

RSTDUR

has elapsed, the 33742

enters the Normal Request operating mode. The Reset mode

is entered if a reset condition occurs (VDD LOW, watchdog

time-out, or watchdog trigger in a closed window).

NORMAL REQUEST MODE

The Normal Request mode is a temporary operating mode

automatically entered by the SBC after the Reset mode or

after the 33742 wakes up from the Stop mode.

After a wake-up from the Sleep mode or after a device

power-up, the SBC enters the Reset mode prior to entering

the Normal Request mode. After a wake-up from the Stop

mode, the 33742 enters the Normal Request mode directly.

In Normal Request mode, the VDD regulator is ON, the V2

regulator is OFF, and the RST pin is HIGH. As soon as the

SBC enters the Normal Request mode, an internal 350 ms

timer is started (parameter t

NRTOUT

). During this time, the

application’s MCU must address the 33742 via SPI and

configure the TIM1 sub register to select the watchdog

period. This is required of the SBC to stop the 350 ms

watchdog timer and enter the Normal or Standby mode and

to set the watchdog timer configuration.

NORMAL REQUEST ENTERED AND NO

WATCHDOG CONFIGURATION OCCURS

If the Normal Request mode is entered after the SBC

powers up or after a wake-up from Stop mode and no

watchdog configuration occurs before the 350 ms time period

has expired, the device enters the Reset mode. If no

watchdog configuration is performed, the 33742 will cycle

from the Normal Request mode to Reset mode to Normal

Request mode.

If the Normal Request mode is entered after a wake-up

from Sleep mode, and no watchdog configuration occurs

while the 33742S is in Normal Request mode, the SBC

returns to the Sleep mode.

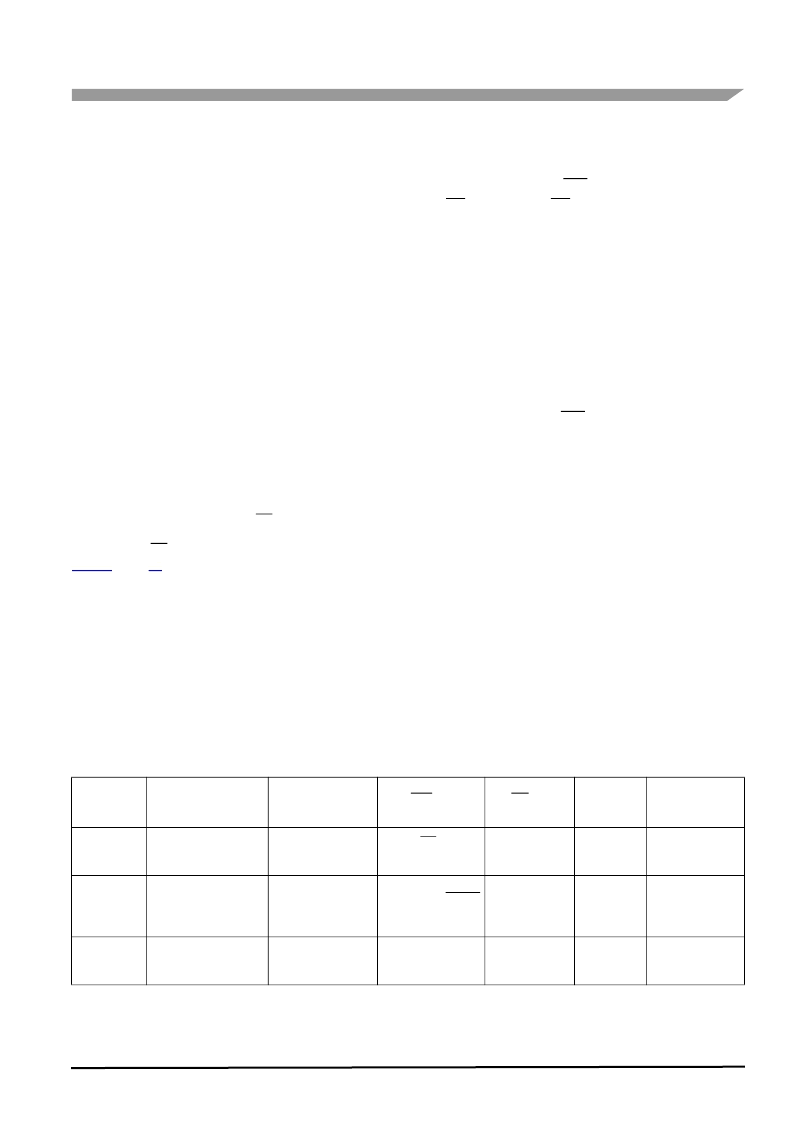

Table 7. Table of Operations

Mode

Voltage Regulator

HS Switch

Wake-Up

Capabilities

(if Enabled)

RST Pin

INT Pin

Watchdog

Software

CAN Cell

Normal

Request

VDD: ON,

V2: OFF,

HS: OFF

–

Low for t

RST

DUR

time,

then HIGH

–

–

–

Normal

VDD: ON,

V2: ON,

HS: Controllable

–

Normally HIGH.

Active LOW if WDOG

or V

DD

undervoltage

occurs

If enabled, signal

failure (VDD

Pre-Warning

Temp, CAN, HS)

Running

TXD RXD

Standby

VDD: ON,

V2: OFF,

HS: Controllable

–

Same as Normal

mode

Same as Normal

mode

Running

Low power

相關PDF資料 |

PDF描述 |

|---|---|

| MCZ33790EG | Two-Channel Distributed System Interface (DSI) Physical Interface Device |

| MCZ33793AEF | Distributed System Interface (DSI) Sensor Interface |

| MCZ33797EK | Four Channel Squib Driver IC |

| MCZ33800EK | Engine Control Integrated Circuit |

| MCZ33879AEK | Configurable Octal Serial Switch with Open Load Detect Current Disable |

相關代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MCZ33742EGR2 | 功能描述:網(wǎng)絡控制器與處理器 IC SBC-E-HS-CAN RoHS:否 制造商:Micrel 產(chǎn)品:Controller Area Network (CAN) 收發(fā)器數(shù)量: 數(shù)據(jù)速率: 電源電流(最大值):595 mA 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:PBGA-400 封裝:Tray |

| MCZ33742SEG | 功能描述:網(wǎng)絡控制器與處理器 IC SBC-E-HS-CAN RoHS:否 制造商:Micrel 產(chǎn)品:Controller Area Network (CAN) 收發(fā)器數(shù)量: 數(shù)據(jù)速率: 電源電流(最大值):595 mA 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:PBGA-400 封裝:Tray |

| MCZ33742SEGR2 | 功能描述:網(wǎng)絡控制器與處理器 IC SBC-E-HS-CAN RoHS:否 制造商:Micrel 產(chǎn)品:Controller Area Network (CAN) 收發(fā)器數(shù)量: 數(shù)據(jù)速率: 電源電流(最大值):595 mA 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:PBGA-400 封裝:Tray |

| MCZ33780EG | 功能描述:多路器開關 IC DBUS MASTER RoHS:否 制造商:Texas Instruments 通道數(shù)量:1 開關數(shù)量:4 開啟電阻(最大值):7 Ohms 開啟時間(最大值): 關閉時間(最大值): 傳播延遲時間:0.25 ns 工作電源電壓:2.3 V to 3.6 V 工作電源電流: 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:UQFN-16 |

| MCZ33780EG | 制造商:Freescale Semiconductor 功能描述:DUAL DBUS MASTER INTERFACE 16SOIC |

發(fā)布緊急采購,3分鐘左右您將得到回復。