- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄371134 > MPC2605ZP66R (MOTOROLA INC) Integrated Secondary Cache for PowerPC Microprocessors PDF資料下載

參數(shù)資料

| 型號(hào): | MPC2605ZP66R |

| 廠商: | MOTOROLA INC |

| 元件分類: | SRAM |

| 英文描述: | Integrated Secondary Cache for PowerPC Microprocessors |

| 中文描述: | 32K X 72 CACHE TAG SRAM, 8.5 ns, PBGA241 |

| 封裝: | PLASTIC, BGA-241 |

| 文件頁數(shù): | 25/30頁 |

| 文件大小: | 288K |

| 代理商: | MPC2605ZP66R |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁當(dāng)前第25頁第26頁第27頁第28頁第29頁第30頁

MPC2605

25

MOTOROLA

TEST ACCESS PORT DESCRIPTION

INSTRUCTION SET

A five pin IEEE Standard 1149.1 Test Port (JTAG) is in-

cluded on this device. When the TAP (Test Access Port) con-

troller is in the SHIFT–IR state, the instruction register is

placed between TDI and TDO. In this state, the desired

instruction would be serially loaded through the TDI input.

TRST resets the TAP controller to the test–logic reset state.

The TAP instruction set for this device are as follows.

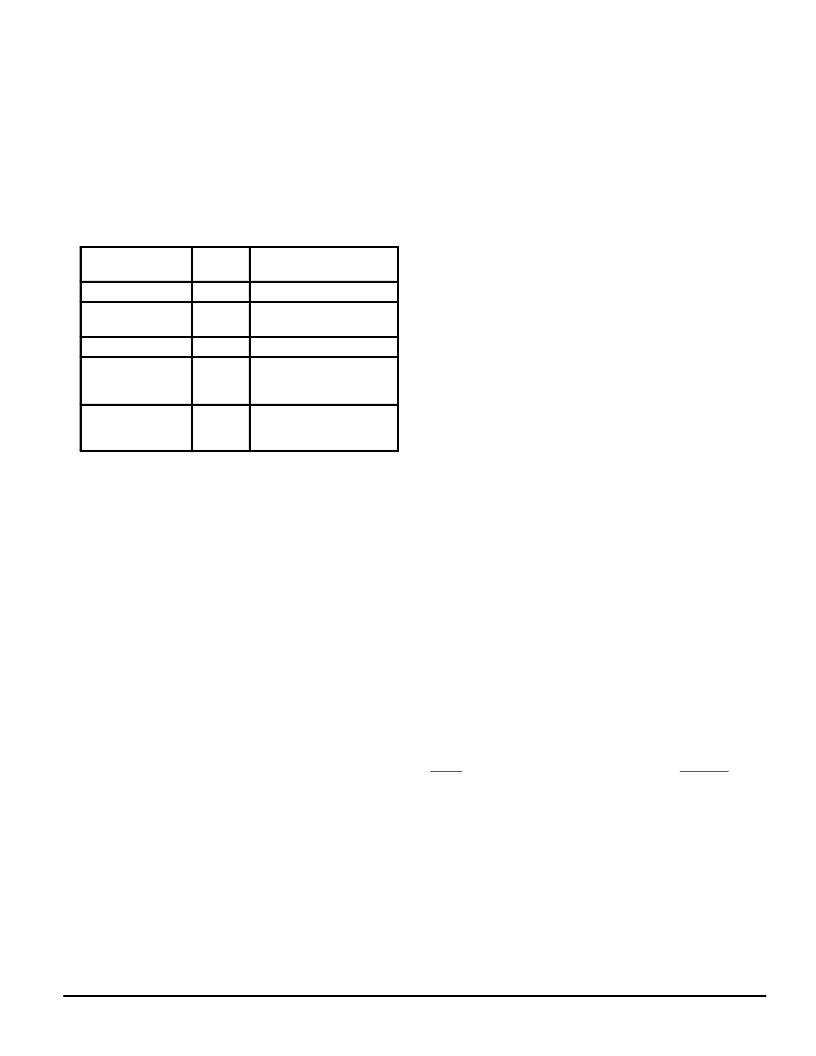

STANDARD INSTRUCTIONS

Instruction

Code

(Binary)

Description

BYPASS

1111*

Bypass instruction

SAMPLE/PRELOAD

0010

Sample and/or preload

instruction

EXTEST

0000

Extest instruction

HIGHZ

1001

High–Z all output pins while

bypass register is between

TDI and TDO

CLAMP

1100

Clamp output pins while

bypass register is between

TDI and TDO

* Default state at power–up.

SAMPLE/PRELOAD TAP INSTRUCTION

The SAMPLE/PRELOAD TAP instruction is used to allow

scanning of the boundary–scan register without causing in-

terference to the normal operation of the chip logic. The

169–bit boundary–scan register contains bits for all device

signal and clock pins and associated control signals. This

register is accessible when the SAMPLE/PRELOAD TAP

instruction is loaded into the TAP instruction register in the

SHIFT–IR state. When the TAP controller is then moved to

the SHIFT–DR state, the boundary–scan register is placed

between TDI and TDO. This scan register can then be used

prior to the EXTEST instruction to preload the output pins

with desired values so that these pins will drive the desired

state when the EXTEST instruction is loaded. As data is writ-

ten into TDI, data also streams out TDO which can be used

to pre–sample the inputs and outputs.

SAMPLE/PRELOAD would also be used prior to the

CLAMP instruction to preload the values on the output pins

that will be driven out when the CLAMP instruction is loaded.

EXTEST TAP INSTRUCTION

The EXTEST instruction is intended to be used in con-

junction with the SAMPLE/PRELOAD instruction to assist in

testing board level connectivity. Normally, the SAMPLE/

PRELOAD instruction would be used to preload all output

pins. The EXTEST instruction would then be loaded. During

EXTEST, the boundary–scan register is placed between TDI

and TDO in the SHIFT–DR state of the TAP controller. Once

the EXTEST instruction is loaded, the TAP controller would

then be moved to the run–test/idle state. In this state, one

cycle of TCK would cause the preloaded data on the output

pins to be driven while the values on the input pins would be

sampled. Note the TCK, not the clock pin (CLK), is used as

the clock input while CLK is only sampled during EXTEST.

After one clock cycle of TCK, the TAP controller would then

be moved to the SHIFT–DR state where the sampled values

would be shifted out of TDO (and new values would be

shifted in TDI). These values would normally be compared to

expected values to test for board connectivity.

CLAMP TAP INSTRUCTION

The CLAMP instruction is provided to allow the state of the

signals driven from the output pins to be determined from the

boundary–scan register while the bypass register is selected

as the serial path between TDI and TDO. The signals driven

from the output pins will not change while the CLAMP

instruction is selected. EXTEST could also be used for this

purpose, but CLAMP shortens the board scan path by insert-

ing only the bypass register between TDI and TDO. To use

CLAMP, the SAMPLE/PRELOAD instruction would be used

first to scan in the values that will be driven on the output pins

when the CLAMP instruction is active.

HIGHZ TAP INSTRUCTION

The HIGH–Z instruction is provided to allow all the outputs

to be placed in an inactive drive state (high–Z). During the

HIGH–Z instruction the bypass register is connected be-

tween TDI and TDO.

BYPASS TAP INSTRUCTION

The BYPASS instruction is the default instruction loaded at

power up. This instruction will place a single shift register

between TDI and TDO during the SHIFT–DR state of the

TAP controller. This allows the board level scan path to be

shortened to facilitate testing of other devices in the scan

path.

DISABLING THE TEST ACCESS PORT AND

BOUNDARY SCAN

It is possible to use this device without utilizing the four

pins used for the test access port. To circuit disable the

device, TCK must be tied to VSS to preclude mid level inputs.

TRST should be tied to VSS to ensure proper HRESET op-

eration. Although TDI and TMS are designed in such a way

that an undriven input will produce a response equivalent to

the application of a logic 1, it is still advisable to tie these

inputs to VDD through a 1K resistor. TDO should remain

unconnected.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MPC500 | ELECTROHYDRAULIC BRAKING |

| MPC555D | This document provides an overview of the MPC555 microcontroller, including a block diagram showing the major modular components and sections that lis |

| MPC555PB | CABLE ASSEMBLY; ; NMO Antenna Mount to BNC Male, RG58C/U, 5 feet |

| MPC555LFAZP40 | This document provides an overview of the MPC555 microcontroller, including a block diagram showing the major modular components and sections that lis |

| MPC555LFMZP40 | Circular Connector; Body Material:Aluminum; Series:PT07; Number of Contacts:6; Connector Shell Size:10; Connecting Termination:Solder; Circular Shell Style:Jam Nut Receptacle; Circular Contact Gender:Socket; Insert Arrangement:10-98 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MPC2605ZP83 | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| MPC27T416TQ9 | 制造商:Motorola 功能描述:MOTOROLA |

| MPC-2C-24VDC | 制造商:Allied Controls Incorporated 功能描述: |

| MPC-2C-5VDC | 制造商:Allied Controls Incorporated 功能描述: |

| MPC-2C-6VDC | 制造商:Allied Controls Incorporated 功能描述: |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。