- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄45342 > MPC5606SVLU6R (FREESCALE SEMICONDUCTOR INC) 32-BIT, FLASH, 64 MHz, MICROCONTROLLER, PQFP176 PDF資料下載

參數(shù)資料

| 型號(hào): | MPC5606SVLU6R |

| 廠商: | FREESCALE SEMICONDUCTOR INC |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 32-BIT, FLASH, 64 MHz, MICROCONTROLLER, PQFP176 |

| 封裝: | 24 X 24 MM, 1.40 MM HEIGHT, 0.50 MM PITCH, ROHS COMPLIANT, MS-026BGA, LQFP-176 |

| 文件頁數(shù): | 99/136頁 |

| 文件大?。?/td> | 858K |

| 代理商: | MPC5606SVLU6R |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁當(dāng)前第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁第128頁第129頁第130頁第131頁第132頁第133頁第134頁第135頁第136頁

MPC5606S Microcontroller Data Sheet, Rev. 7

Freescale Semiconductor

65

3.6.4.2

Static latch-up (LU)

Two complementary static tests are required on six parts to assess the latch-up performance:

A supply overvoltage is applied to each power supply pin.

A current injection is applied to each input, output and configurable I/O pin.

These tests are compliant with the EIA/JESD 78 IC latch-up standard.

3.7

Power management electrical characteristics

3.7.1

Voltage regulator electrical characteristics

The internal high power or main regulator (HPREG) requires an external NPN ballast transistor (see Table 21 and Table 22) to

be connected as shown in Figure 7 as well as an external capacitance (CREG) to be connected to the device in order to provide

a stable low voltage digital supply to the device. Capacitances should be placed on the board as near as possible to the associated

pins. Care should also be taken to limit the serial inductance of the board to less than 15 nH.

For the MPC5606S microcontroller, 100 nF should be placed between each of the VDD12/VSS12 supply pairs and also between

the VDDPLL/VSSPLL pair. These decoupling capacitors are in addition to the required stability capacitance. Additionally, 10 F

should be placed between the VDDR pin and the adjacent VSS pin.

VDDR = 3.0 V to 3.6 V / 4.5 V to 5.5 V, TA = 40 to 105 °C, unless otherwise specified.

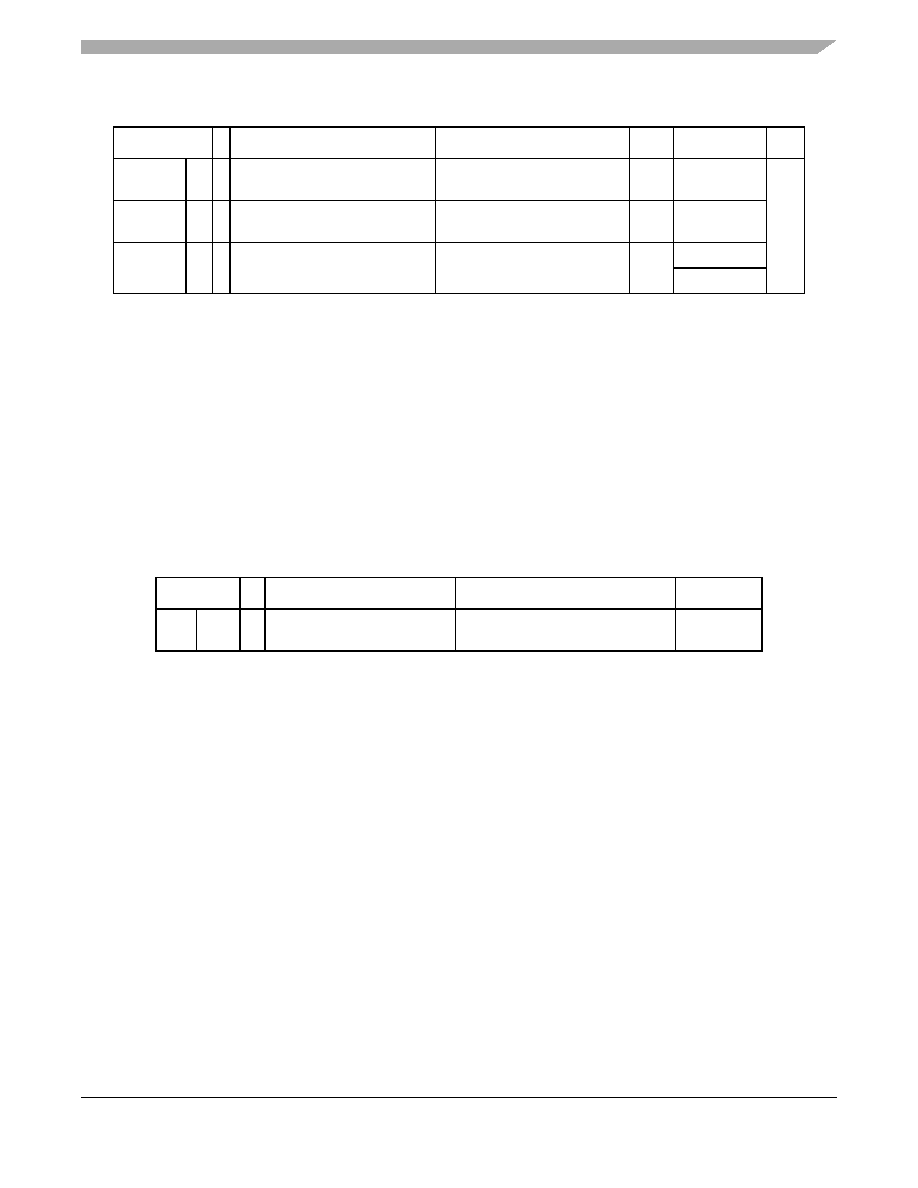

Table 19. ESD absolute maximum ratings1 2

1 All ESD testing is in conformity with CDF-AEC-Q100 Stress Test Qualification for Automotive Grade Integrated

Circuits.

2 A device will be defined as a failure if after exposure to ESD pulses the device no longer meets the device

specification requirements. Complete DC parametric and functional testing shall be performed per applicable

device specification at room temperature followed by hot temperature, unless specified otherwise in the device

specification.

Symbol

C

Ratings

Conditions

Class

Max value

Unit

VESD(HBM) CC T Electrostatic discharge voltage

(Human Body Model)

TA = 25 °C

conforming to AEC-Q100-002

H1C

2000

V

VESD(MM) CC T Electrostatic discharge voltage

(Machine Model)

TA = 25 °C

conforming to AEC-Q100-003

M2

200

VESD(CDM) CC T Electrostatic discharge voltage

(Charged Device Model)

TA = 25 °C

conforming to AEC-Q100-011

C3A

500

750 (corners)

Table 20. Latch-up results

Symbol

C

Parameter

Conditions

Class

LU

CC

T Static latch-up class

TA = 105 °C

conforming to JESD 78

II level A

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MPC5606SVLU6 | 32-BIT, FLASH, 64 MHz, MICROCONTROLLER, PQFP176 |

| MPC5606SCLQ6R | 32-BIT, FLASH, 64 MHz, MICROCONTROLLER, PQFP144 |

| MPC5607BCLQ6R | FLASH, 64 MHz, MICROCONTROLLER, PQFP144 |

| MPC5607BVLL4R | FLASH, 48 MHz, MICROCONTROLLER, PQFP100 |

| MPC5607BCMG4 | FLASH, 48 MHz, MICROCONTROLLER, PBGA208 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MPC5607B | 制造商:Freescale Semiconductor 功能描述: |

| MPC5607B_13 | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:MicrocontrollerData Sheet |

| MPC5607BECLLR | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:Microcontroller |

| MPC5607BECLQR | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:Microcontroller |

| MPC5607BECLUR | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:Microcontroller |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。