- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄369993 > pentium III CPU (Intel Corp.) Pentium III Processor for the SC242 at 450MHz to 1.0GHz(SC242工作頻率450MHZ到1GHZ奔III處理器) PDF資料下載

參數(shù)資料

| 型號(hào): | pentium III CPU |

| 廠商: | Intel Corp. |

| 英文描述: | Pentium III Processor for the SC242 at 450MHz to 1.0GHz(SC242工作頻率450MHZ到1GHZ奔III處理器) |

| 中文描述: | 奔騰III處理器在450MHz至1.0GHz的(SC242工作頻率至450MHz到1GHz的奔三處理器的SC242) |

| 文件頁(yè)數(shù): | 34/102頁(yè) |

| 文件大小: | 920K |

| 代理商: | PENTIUM III CPU |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)當(dāng)前第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)第94頁(yè)第95頁(yè)第96頁(yè)第97頁(yè)第98頁(yè)第99頁(yè)第100頁(yè)第101頁(yè)第102頁(yè)

34

Datasheet

Pentium

III Processor for the SC242 at 450 MHz to 1.0 GHz

NOTES:

1. Unless otherwise noted, all specifications in this table apply to all Pentium

III processor frequencies.

2. These specifications are tested during manufacturing.

3. All AC timings for the CMOS signals are referenced to the BCLK rising edge at 0.7 V at the processor core

pins. All CMOS signal timings (compatibility signals, etc.) are referenced at 1.25 V.

4. These signals may be driven asynchronously.

5. When driven inactive or after V

CCCORE

, V

CCL2

/V

CC3.3

, and BCLK become stable.

NOTES:

1. Unless otherwise noted, all specifications in this table apply to all Pentium

III processor frequencies.

.

NOTES:

1. Unless otherwise noted, all specifications in this table apply to all Pentium

III processor frequencies.

2. These specifications are tested during manufacturing.

3. All AC timings for the APIC I/O signals are referenced to the PICCLK rising edge at 1.25 V at the processor

core pins. All APIC I/O signal timings are referenced at 1.25 V (CPUID 067xh) or 0.75 V (CPUID 068xh) at

the processor core pins.

4. Referenced to PICCLK rising edge.

5. For open drain signals, valid delay is synonymous with float delay.

6. Valid delay timings for these signals are specified into a 150

load pulled up to 2.5 V +5%.

7. This specification applies to the Pentium

III processor with CPUID=067xh.

8. This specification applies to the Pentium

III processor with CPUID=068xh.

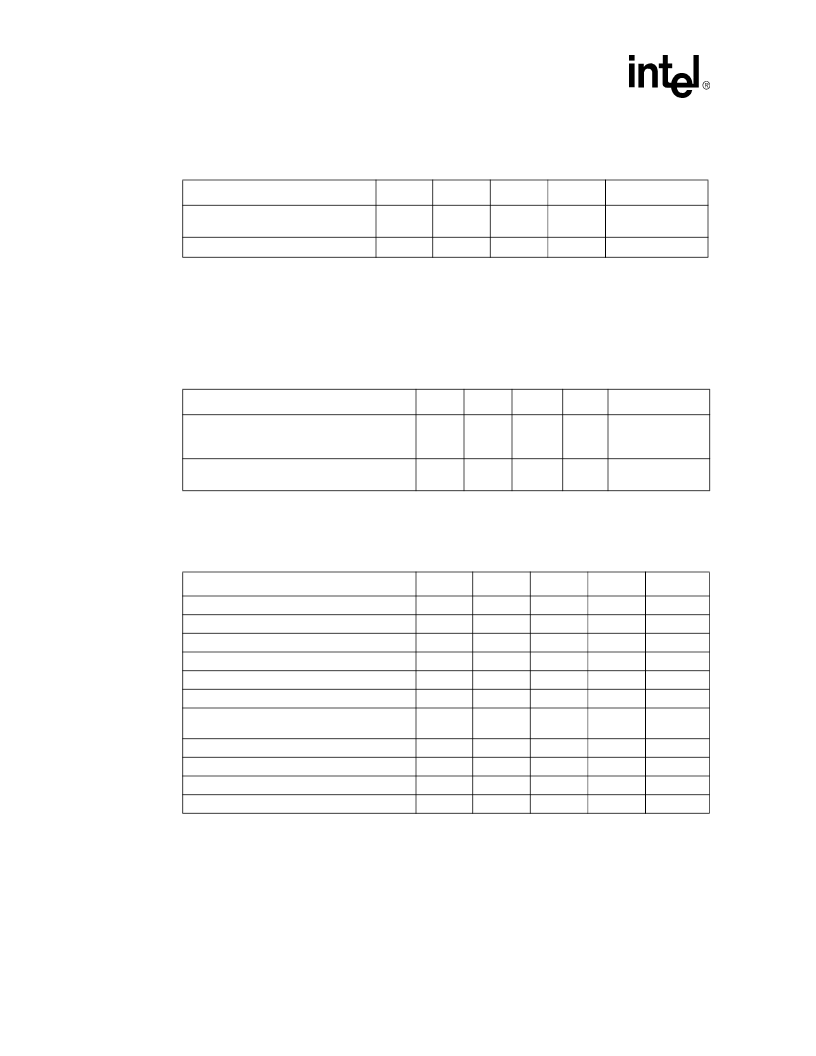

Table 15. System Bus AC Specifications (CMOS Signal Group) at the

Processor Core Pins

1, 2, 3, 4

T# Parameter

Min

Max

Unit

Figure

Notes

T14: CMOS Input Pulse Width, except

PWRGOOD

2

BCLKs

8

Active and Inactive

states

T15: PWRGOOD Inactive Pulse Width

10

BCLKs

8

,

11

5

Table 16. System Bus AC Specifications (Reset Conditions)

1

T# Parameter

Min

Max

Unit

Figure

Notes

T16: Reset Configuration Signals

(A[14:5]#, BR0#, FLUSH#,

INIT#) Setup Time

4

BCLKs

10

Before deassertion

of RESET#

T17: Reset Configuration Signals (A[14:5]#,

BR0#, FLUSH#, INIT#) Hold Time

2

20

BCLKs

10

After clock that

deasserts RESET#

Table 17. System Bus AC Specifications (APIC Clock and APIC I/O) at the

Processor Core Pins

1, 2, 3

T# Parameter

Min

Max

Unit

Figure

Notes

T21: PICCLK Frequency

2.0

33.3

MHz

T22: PICCLK Period

30.0

500.0

ns

7

T23: PICCLK High Time

12.0

ns

7

T24: PICCLK Low Time

12.0

ns

7

T25: PICCLK Rise Time

0.25

3.0

ns

7

T26: PICCLK Fall Time

0.25

3.0

ns

7

T27: PICD[1:0] Setup Time

8.0

5.0

ns

ns

9

9

4, 7

4, 8

T28: PICD[1:0] Hold Time

2.5

ns

9

4

T29: PICD[1:0] Valid Delay

1.5

10

ns

8

4, 5, 6, 7

T29a: PICD[1:0] Valid Delay (Rising Edge)

1.5

8.7

ns

8

4, 5, 6, 8

T29b: PICD[1:0] Valid Delay (Falling Edge)

1.5

12.0

ns

8

4, 5, 6, 8

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| pentium III processor | 32 bit Processor Mobile Module(32 位帶移動(dòng)模塊處理器) |

| Pentium OverDrive Processor | Pentium OverDrive Processor With MMX Technology For Pentium Processor-Based System(帶MMX技術(shù)奔騰超速轉(zhuǎn)動(dòng)處理器) |

| pentium pro processor | Pentium Pro Processor with 1MB L2 Cache at 200MHZ(1兆比特L2高速緩存頻率200兆赫茲處理器) |

| pentium processor with MMX | 32-bit processor with MMX technology(32位帶MMX技術(shù)處理器) |

| pentium processor | 32 Bit Processor With MMX And Mobile Module(32位帶移動(dòng)模塊和MMX技術(shù)CPU) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| P-ENV568K3G3 | 制造商:Panasonic Industrial Company 功能描述:TUNER |

| PEO14012 | 制造商:TE Connectivity 功能描述:RELAY SPCO 12VDC |

| PEO14024 | 制造商:TE Connectivity 功能描述:RELAY SPCO 24VDC |

| PEO96742 | 制造商:Delphi Corporation 功能描述:ASM TERM |

| PEOODO3A | 制造商:MACOM 制造商全稱(chēng):Tyco Electronics 功能描述:Versatile Power Entry Module with Small Footprint |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。