- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄373274 > RIVA 128ZX (意法半導(dǎo)體) 128-Bit 3D Multimedia Accelerator(128位3D多媒體加速器) PDF資料下載

參數(shù)資料

| 型號: | RIVA 128ZX |

| 廠商: | 意法半導(dǎo)體 |

| 英文描述: | 128-Bit 3D Multimedia Accelerator(128位3D多媒體加速器) |

| 中文描述: | 128位3D多媒體加速器(128位三維多媒體加速器) |

| 文件頁數(shù): | 63/85頁 |

| 文件大小: | 608K |

| 代理商: | RIVA 128ZX |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁當(dāng)前第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁

128-BIT 3D MULTIMEDIA ACCELERATOR

RIVA128ZX

63/85

12

The RIVA128ZX has a number of features designed to support in-circuit board testing. These include:

Dedicated test mode input and dual-function test mode select pins selecting the following modes:

-

Pin float

-

Parametric NAND tree

-

All outputs driven high

-

All outputs driven low

Checksum test

Test registers

IN-CIRCUIT BOARD TESTING

12.1 TEST MODES

Primary test control is provided by the dedicated

TESTMODE

input pin. The RIVA128ZX is in normal op-

erating mode whenthis pin is deasserted. When

TESTMODE

is asserted,

MP_AD[3:0]

are reassigned as

TESTCTL[3:0]

respectively. Test modes are selected asynchronously through a combination of the pin

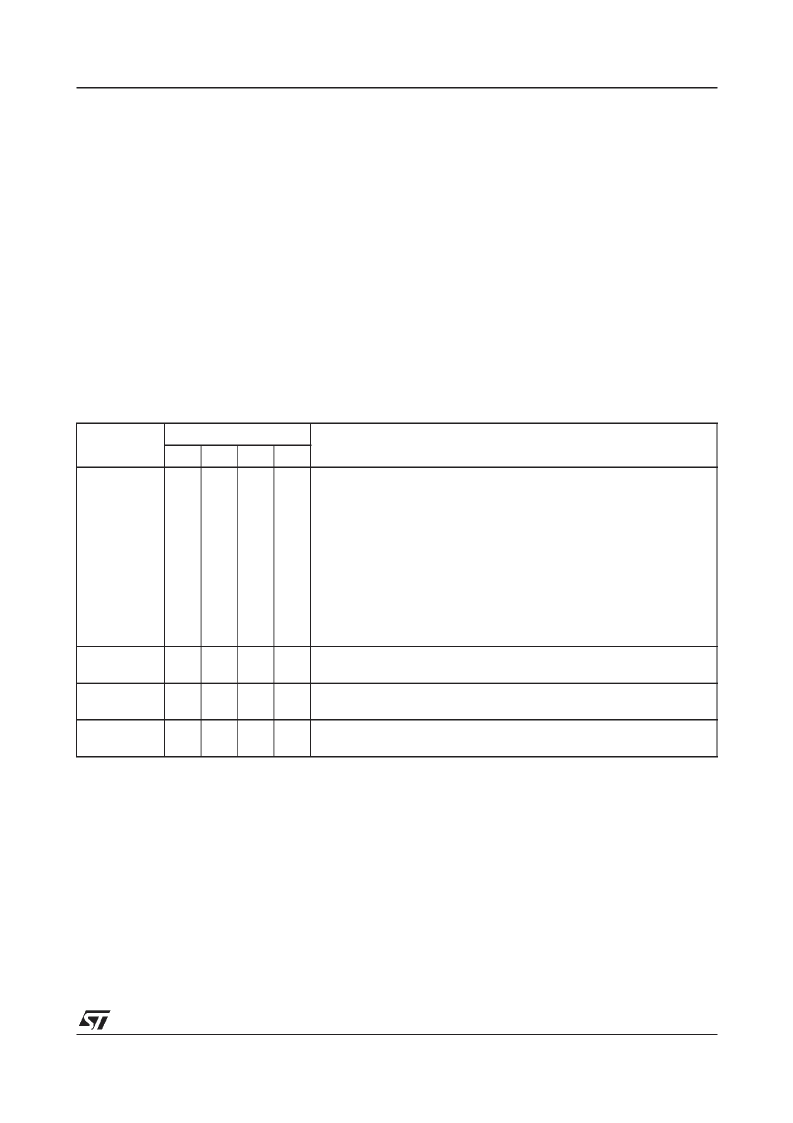

states shown in Table 21.

Table 21.

Test mode selection and descriptions

Test mode

TESTCTL[3:0]

12.2 CHECKSUM TEST

The RIVA128ZX hardware checksum feature sup-

ports testing of the entire pixel datapath at full video

rates fromthe framebufferthrough totheDACinputs.

Each of the three RGB colors can be tested to pro-

vide a correlation between the intended and actual

display. Checksums are accumulated during active

(unblanked) display.Note that the checksum mech-

anism does not check the DAC outputs (i.e. what is

physically being displayedon the monitor).

For a given image (which can be a real application’s

image or aspeciallyprepared testcard), theoretical-

ly derived checksum values can be calculated for a

selected RGB color, which are then compared with

the RIVA128ZXhardware checksum value.Alterna-

tively the checksum value from a known good chip

can be used as the reference.

Hardwarechecksum accumulation is notaffectedby

the horizontal and vertical synchronization wave-

forms or timings. Any discrepancy between the cal-

culated and RIVA128ZX hardware accumulated

checksum values therefore indicates a problem in

the device or system being tested. Details of pro-

gramming the RIVA128ZX checksum are given in

the RIVA128ZX

Programming Reference Manual

[2].

Description

3

2

1

0

Parametric

NAND tree

1

0

1

0

A single parametric NAND tree is provided to give a quiescent environ-

ment in which to test VIL and VIH without requiring core activity.

This capability is provided in the pads by chaining all I and I/O paths to-

gether via two input NAND gates. The chain begins with one input of the

firstNAND gate tied to VDD while the other input is connected to the first

devicepin on the NAND tree. The output of this gate then becomes the in-

put of the next NAND gate in the tree and so on until all pad input paths

havebeen connected.The finalNAND gate output is connected to an out-

put-only pin whose normal functionality is disabled in NAND tree mode.

The NAND treelength is therefore equal to the number of I and I/O pins in

the RIVA128ZX. Output -only pins are not connected into the NAND tree.

Pin float

1

1

0

0

All pin output drivers are tristated in this test mode so that pin leakage

current (IIL,IIH,IOZL,IOZH) can be measured.

Outputs high

1

1

1

0

All pin output drivers drive a high output state in this test mode so that

output high voltage (VOH at IOH) can be measured.

Outputs low

1

1

1

1

All pin output drivers drive a low output state in this test mode so that out-

put low voltage(VOL at IOL) can be measured.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| RIVA128ZX | 128-BIT 3D MULTIMEDIA ACCELERATOR |

| RIVA128 | RIVA 128⑩ 128-BIT 3D MULTIMEDIA ACCELERATOR |

| RIX-0142-H | FILTER IEC EINGANG ULTRA KOMPAKT 1A |

| RIX-0342-H | FILTER IEC EINGANG ULTRA KOMPAKT 3A |

| RIX-0642-H | FILTER IEC EINGANG ULTRA KOMPAKT 6A |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| RIVCF256H | 制造商:STEC Inc 功能描述:256MB COMPACT FLASH - Bulk |

| RIVET DPG FLOAT MTG | 制造商:ITT Interconnect Solutions 功能描述:Rack & Panel |

| RIVET(SSR389) | 制造商: 功能描述: 制造商:undefined 功能描述: |

| RIVET-DPD-PIN-INSERT-SPCR | 制造商:ITT Interconnect Solutions 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。