- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄373435 > SN54ABT8373 (Texas Instruments, Inc.) Scan Test Devices With Octal D-Type Latches(掃描測試裝置(帶八D鎖存器)) PDF資料下載

參數(shù)資料

| 型號: | SN54ABT8373 |

| 廠商: | Texas Instruments, Inc. |

| 英文描述: | Scan Test Devices With Octal D-Type Latches(掃描測試裝置(帶八D鎖存器)) |

| 中文描述: | 掃描測試設備與八路D類鎖存器(掃描測試裝置(帶八?鎖存器)) |

| 文件頁數(shù): | 14/19頁 |

| 文件大小: | 391K |

| 代理商: | SN54ABT8373 |

SN54ABT8373, SN74ABT8373

SCAN TEST DEVICES WITH OCTAL D-TYPE LATCHES

SCBS487 – JULY 1994

3–14

POST OFFICE BOX 655303

DALLAS, TEXAS 75265

timing description

All test operations of the

′

ABT8373 are synchronous to TCK. Data on the TDI, TMS, and normal-function inputs

is captured on the rising edge of TCK. Data appears on the TDO and normal-function output pins on the falling

edge of TCK. The TAP controller is advanced through its states (as illustrated in Figure 1) by changing the value

of TMS on the falling edge of TCK and then applying a rising edge to TCK.

A simple timing example is illustrated in Figure 8. In this example, the TAP controller begins in the

Test-Logic-Reset state and is advanced through its states as necessary to perform one instruction-register scan

and one data-register scan. While in the Shift-IR and Shift-DR states, TDI is used to input serial data, and TDO

is used to output serial data. The TAP controller is then returned to the Test-Logic-Reset state. Table 5 explains

the operation of the test circuitry during each TCK cycle.

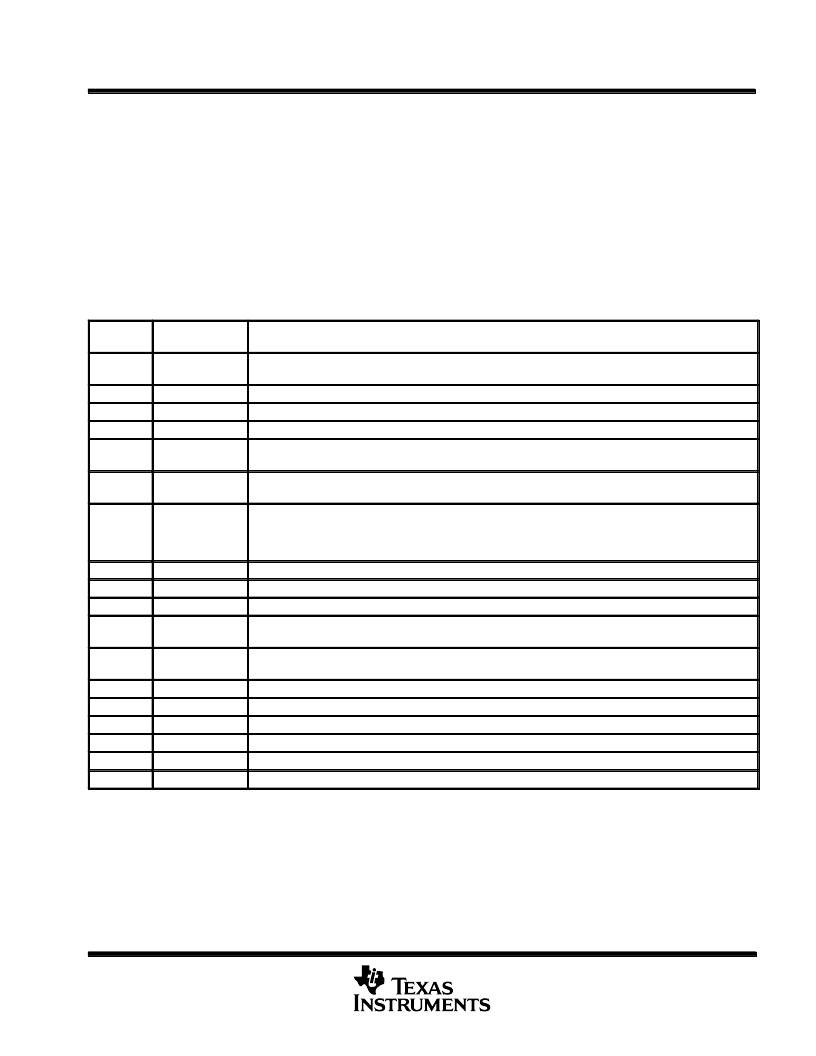

Table 5. Explanation of Timing Example

TCK

CYCLE(S)

TAP STATE

AFTER TCK

DESCRIPTION

1

Test-Logic-Reset

TMS is changed to a logic 0 value on the falling edge of TCK to begin advancing the TAP controller toward

the desired state.

2

Run-Test/Idle

3

Select-DR-Scan

4

Select-IR-Scan

5

Capture-IR

The IR captures the 8-bit binary value 10000001 on the rising edge of TCK as the TAP controller exits the

Capture-IR state.

6

Shift-IR

TDO becomes active and TDI is made valid on the falling edge of TCK. The first bit is shifted into the TAP on

the rising edge of TCK as the TAP controller advances to the next state.

7–13

Shift-IR

One bit is shifted into the IR on each TCK rising edge. With TDI held at a logic 1 value, the 8-bit binary value

11111111 is serially scanned into the IR. At the same time, the 8-bit binary value 10000001 is serially scanned

out of the IR via TDO. In TCK cycle 13, TMS is changed to a logic 1 value to end the IR scan on the next TCK

cycle. The last bit of the instruction is shifted as the TAP controller advances from Shift-IR to Exit1-IR.

14

Exit1-IR

TDO becomes inactive (goes to the high-impedance state) on the falling edge of TCK.

15

Update-IR

The IR is updated with the new instruction (BYPASS) on the falling edge of TCK.

16

Select-DR-Scan

17

Capture-DR

The bypass register captures a logic 0 value on the rising edge of TCK as the TAP controller exits the

Capture-DR state.

18

Shift-DR

TDO becomes active and TDI is made valid on the falling edge of TCK. The first bit is shifted into the TAP on

the rising edge of TCK as the TAP controller advances to the next state.

19–20

Shift-DR

The binary value 101 is shifted in via TDI, while the binary value 010 is shifted out via TDO.

21

Exit1-DR

TDO becomes inactive (goes to the high-impedance state) on the falling edge of TCK.

22

Update-DR

In general, the selected data register is updated with the new data on the falling edge of TCK.

23

Select-DR-Scan

24

Select-IR-Scan

25

Test-Logic-Reset

Test operation completed

P

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| SN74ABT8373 | Scan Test Devices With Octal D-Type Latches(掃描測試裝置(帶八D鎖存器)) |

| SN54ABT8374 | Scan Test Devices With Octal D-Type Edge-Triggered Flip-Flops(掃描測試裝置(帶八D邊沿觸發(fā)器)) |

| SN74ABT8374 | Scan Test Devices With Octal D-Type Edge-Triggered Flip-Flops(掃描測試裝置(帶八D邊沿觸發(fā)器)) |

| SN54ABT845 | Octal Bus Interface D-Type Latches With 3-State Outputs(八總線接口D鎖存器(三態(tài)輸出)) |

| SN74ABT845 | Octal Bus Interface D-Type Latches With 3-State Outputs(八總線接口D觸發(fā)器(三態(tài)輸出)) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| SN54ABT841 | 制造商:TI 制造商全稱:Texas Instruments 功能描述:10-BIT BUS-INTERFACE D-TYPE LATCHES WITH 3-STATE OUTPUTS |

| SN54ABT841FK | 制造商:TI 制造商全稱:Texas Instruments 功能描述:10-BIT BUS-INTERFACE D-TYPE LATCHES WITH 3-STATE OUTPUTS |

| SN54ABT841JT | 制造商:TI 制造商全稱:Texas Instruments 功能描述:10-BIT BUS-INTERFACE D-TYPE LATCHES WITH 3-STATE OUTPUTS |

| SN54ABT841W | 制造商:TI 制造商全稱:Texas Instruments 功能描述:10-BIT BUS-INTERFACE D-TYPE LATCHES WITH 3-STATE OUTPUTS |

| SN54ABT843 | 制造商:TI 制造商全稱:Texas Instruments 功能描述:9-BIT BUS-INTERFACE D-TYPE LATCHES WITH 3-STATE OUTPUTS |

發(fā)布緊急采購,3分鐘左右您將得到回復。