- 您現(xiàn)在的位置:買(mǎi)賣IC網(wǎng) > PDF目錄385939 > TMPR4955 (Toshiba Corporation) 64-bit RISC (Reduced Instruction Set Computer) microprocessor(64位精簡(jiǎn)指令集系統(tǒng)計(jì)算機(jī)微處理器) PDF資料下載

參數(shù)資料

| 型號(hào): | TMPR4955 |

| 廠商: | Toshiba Corporation |

| 英文描述: | 64-bit RISC (Reduced Instruction Set Computer) microprocessor(64位精簡(jiǎn)指令集系統(tǒng)計(jì)算機(jī)微處理器) |

| 中文描述: | 64位RISC(精簡(jiǎn)指令集計(jì)算機(jī))微處理器(64位精簡(jiǎn)指令集系統(tǒng)計(jì)算機(jī)微處理器) |

| 文件頁(yè)數(shù): | 26/60頁(yè) |

| 文件大小: | 244K |

| 代理商: | TMPR4955 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)當(dāng)前第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)

TOSHIBA

TENTATIVE

TMPR4955/56

20-Oct.-1999

26

5.7 Processor Request and External Request Protocol

This section explains the bus arbitration protocol for both processor requests and external requests on a

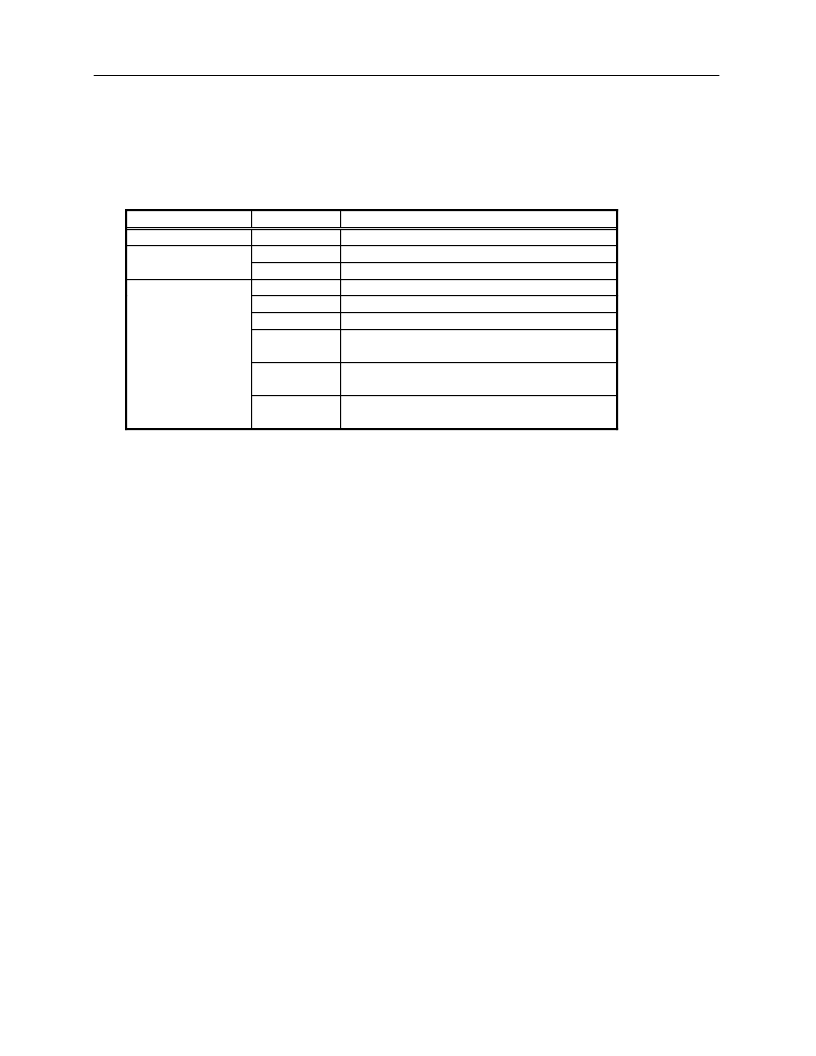

cycle-by-cycle basis. Table 7-1 below describes the abbreviations used in the following timing diagram of

the bus.

Range

Abbreviation

Unsd

Addr

Data<n>

Cmd

Read

Write

SINull

Meaning

Total

SysAD bus

Unused

Physical address

Data number

n

of the data block

Undefined system interface command

Processor or external read request command

Processor or external write request command

External null request command that releases

the system interface

Non-coherent data identifier for datum other

than the final datum

Non-coherent data identifier for the final

datum

NData

SysCmd bus

NEOD

Table 7-1 System Interface Request

5.7.1

Processor request protocol

Processor request protocol is as follows.

Read

Write

Null write

5.7.2

Processor read request protocol

The processor read request protocol is as described in the following sequence. The next step numbers

correspond to the numbers in Figure 7-1.

1.

RdRdy* is asserted to Low by the external agent. This means that the external agent is ready to

accept read requests.

2.

When the system interface is in the master state, the read command is transmitted to the SysCmd bus,

then the processor read request is issued by transmitting the read address to the SysAD bus.

3.

At the same time, the processor asserts the ValidOut* signal for one cycle. This means that valid data

are being transmitted to the SysCmd bus and SysAD bus.

4.

The processor goes into the slave state by itself either at the issue cycle of a read request or after the

Release* signal is asserted for one cycle and the issue cycle of the read request is complete.

Note:

The external agent must not assert the ExtRqst* signal as a means of returning a read

response. It must however wait to shift to the slave state on its own. If an external

request other than a read response is issued, ExtRqst* can be asserted either before the

read response or in the process of the read response.

5.

The SysCmd bus and SysAD bus are released from the processor one cycle after the Release* signal

is asserted.

6.

The SysCmd bus and SysAD bus are driven by the external agent within two cycles after the

Release* signal is asserted.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| TMPR4956F | 64-bit RISC (Reduced Instruction Set Computer) microprocessor(64位精簡(jiǎn)指令集系統(tǒng)計(jì)算機(jī)微處理器) |

| TMPZ84C015AF | C-MOS 8-BIT MICROPROCCESSOR |

| TMPZ84C61AP-6 | TLCS-Z80 CGC : Z80 CLOCK GENERATOR/CONTROLLER |

| TMS2716 | 2048-WORD BY 8-BIT ERASABLE PROGRAMMABLE READ-ONLY MEMORIES |

| TMS2716-30 | 2048-WORD BY 8-BIT ERASABLE PROGRAMMABLE READ-ONLY MEMORIES |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| TMPR4955A | 制造商:TOSHIBA 制造商全稱:Toshiba Semiconductor 功能描述:64-Bit TX System RISC TX49 Family |

| TMPR4955AF | 制造商:TOSHIBA 制造商全稱:Toshiba Semiconductor 功能描述:64-Bit TX System RISC TX49 Family |

| TMPR4955AF-167 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Microcontroller |

| TMPR4955AF-200 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:MICROPROCESSOR|64-BIT|CMOS|QFP|160PIN|PLASTIC |

| TMPR4955B | 制造商:TOSHIBA 制造商全稱:Toshiba Semiconductor 功能描述:64-Bit TX System RISC TX49 Family |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。