- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄385939 > TMPR4955 (Toshiba Corporation) 64-bit RISC (Reduced Instruction Set Computer) microprocessor(64位精簡(jiǎn)指令集系統(tǒng)計(jì)算機(jī)微處理器) PDF資料下載

參數(shù)資料

| 型號(hào): | TMPR4955 |

| 廠商: | Toshiba Corporation |

| 英文描述: | 64-bit RISC (Reduced Instruction Set Computer) microprocessor(64位精簡(jiǎn)指令集系統(tǒng)計(jì)算機(jī)微處理器) |

| 中文描述: | 64位RISC(精簡(jiǎn)指令集計(jì)算機(jī))微處理器(64位精簡(jiǎn)指令集系統(tǒng)計(jì)算機(jī)微處理器) |

| 文件頁(yè)數(shù): | 29/60頁(yè) |

| 文件大小: | 244K |

| 代理商: | TMPR4955 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)當(dāng)前第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)

TOSHIBA

TENTATIVE

TMPR4955/56

20-Oct.-1999

29

With later G2SConfig-Regster, these modes are selected.

1.

R4000 compatible write

2.

Reissue write

3.

Pipeline write

1.

R4000 compatible write

When in the R400 compatible write mode, 4 cycles are required for single write operation. After the

address is asserted for 1 cycle, it is followed by 2 cycles of dummy data. This applies whether in the

64-bit bus mode or the 32-bit bus mode. Figure 7-3 illustrates its basic operation.

In the case of the TX4956, the WrRdy* signal must be asserted for 1 cycle 2 cycles before the write

operation is issued. When in the R4000 compatible signal write mode, the external agent receives the

write data then immediately asserts WrRdy*, making it possible to stop write operation that continues

after 4 cycles. The 2 cycles of dummy data that follow these write data give the external agent time

to stop the next write operation.

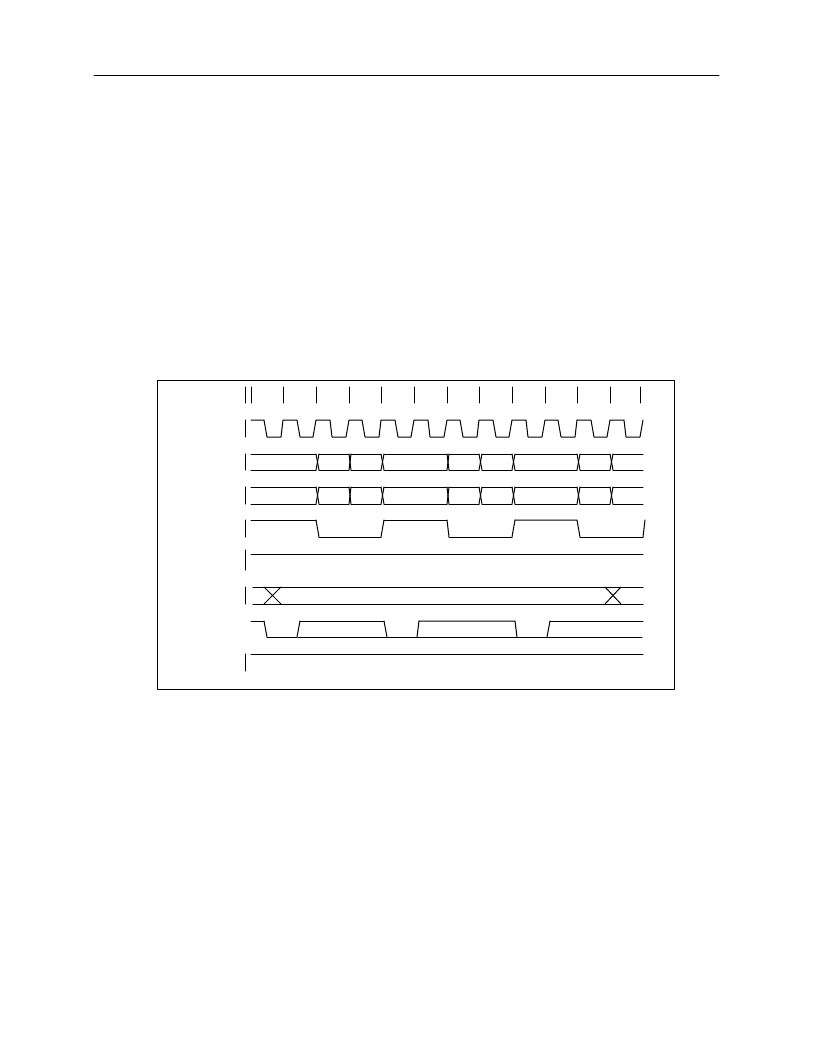

Figure 7-3 R4000 Compatible Write

2.

Reissue write

When in the reissue write mode, the WrRdy* signal is asserted for 1 cycle 2 cycles before the address

cycle, and the write operation is reissued when the WrRdy* signal is asserted during the address

cycle. Figure 7-4 illustrates the reissue write protocol.

By asserting (Low) the WrRdy* signal in the first and third cycles, Addr0/Data0 issues a write

operation in the third or fourth cycle.

By deasserting (High) the WrRdy* signal in the fifth cycle, Addr1/Data1 does not issue a write

operation in the fifth and sixth cycles.

By asserting (Low) the WrRdy* signal again in the eighth and tenth cycles, Addr1/Data issues a

write operation in the tenth and eleventh cycles.

Master

Clock

SysAD bus

Cycle

SysCmd bus

ValidOut*

ValidIn*

RdRdy*

WrRdy*

Release*

1

2

4

5

6

7

8

9

3

11

12

10

Addr

Addr

Addr

Write

Write

Write

Data0

Data1

NEOD

NEOD

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| TMPR4956F | 64-bit RISC (Reduced Instruction Set Computer) microprocessor(64位精簡(jiǎn)指令集系統(tǒng)計(jì)算機(jī)微處理器) |

| TMPZ84C015AF | C-MOS 8-BIT MICROPROCCESSOR |

| TMPZ84C61AP-6 | TLCS-Z80 CGC : Z80 CLOCK GENERATOR/CONTROLLER |

| TMS2716 | 2048-WORD BY 8-BIT ERASABLE PROGRAMMABLE READ-ONLY MEMORIES |

| TMS2716-30 | 2048-WORD BY 8-BIT ERASABLE PROGRAMMABLE READ-ONLY MEMORIES |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| TMPR4955A | 制造商:TOSHIBA 制造商全稱:Toshiba Semiconductor 功能描述:64-Bit TX System RISC TX49 Family |

| TMPR4955AF | 制造商:TOSHIBA 制造商全稱:Toshiba Semiconductor 功能描述:64-Bit TX System RISC TX49 Family |

| TMPR4955AF-167 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Microcontroller |

| TMPR4955AF-200 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:MICROPROCESSOR|64-BIT|CMOS|QFP|160PIN|PLASTIC |

| TMPR4955B | 制造商:TOSHIBA 制造商全稱:Toshiba Semiconductor 功能描述:64-Bit TX System RISC TX49 Family |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。