- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄300038 > TMS570LS10216ASZWTQR (TEXAS INSTRUMENTS INC) 32-BIT, FLASH, 160 MHz, RISC MICROCONTROLLER, PBGA337 PDF資料下載

參數(shù)資料

| 型號: | TMS570LS10216ASZWTQR |

| 廠商: | TEXAS INSTRUMENTS INC |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 32-BIT, FLASH, 160 MHz, RISC MICROCONTROLLER, PBGA337 |

| 封裝: | GERRN, PLASTIC, NFBGA-337 |

| 文件頁數(shù): | 84/102頁 |

| 文件大小: | 1146K |

| 代理商: | TMS570LS10216ASZWTQR |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁當前第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁

PRODUCTPREVIEW

SPNS141D – AUGUST 2010 – REVISED JANUARY 2011

www.ti.com

7.10 SPI Slave Mode Timing Parameters

7.10.1 SPI Slave Mode External Timing Parameters (CLOCK PHASE = 0, SPICLK = input,

SPISIMO = input, and SPISOMI = output)

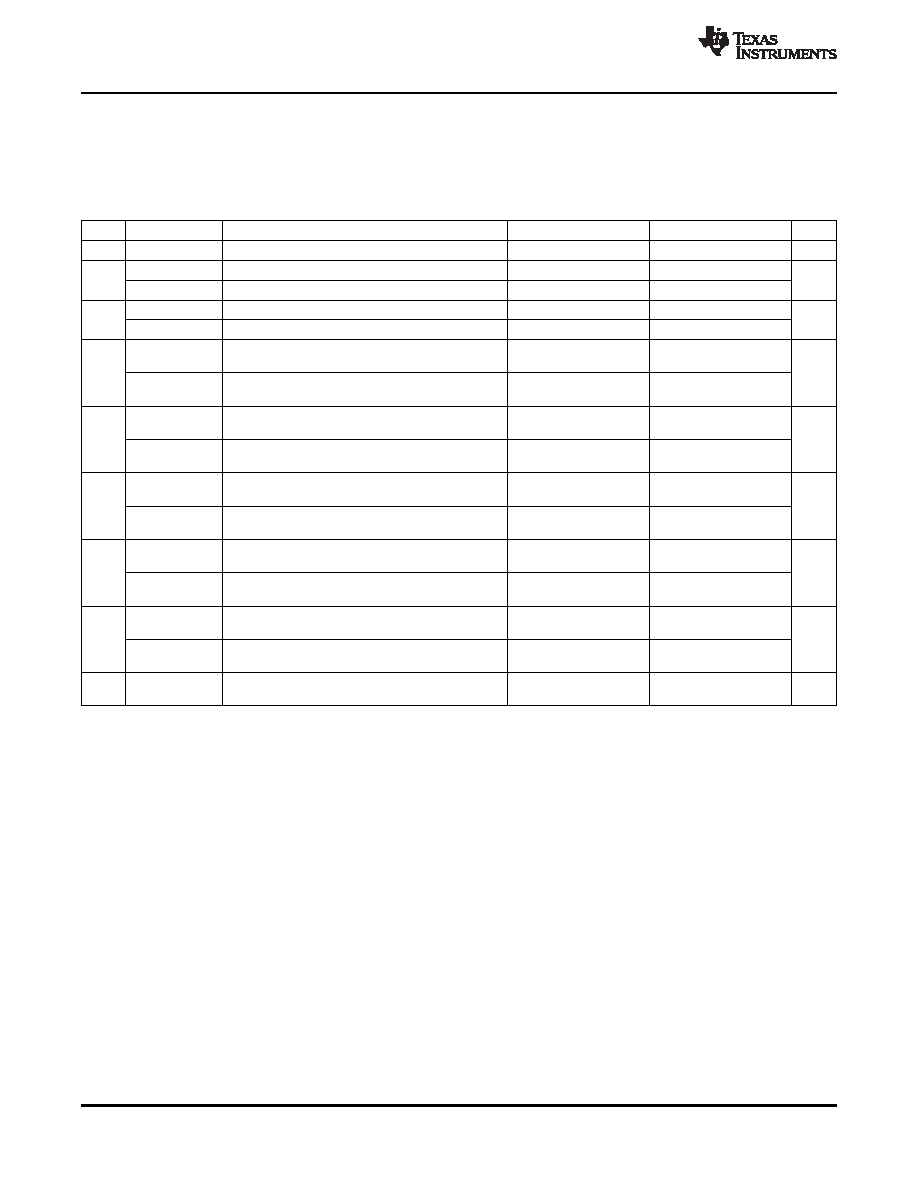

Table 7-15. SPI Slave Mode External Timing Parameters (1)(2)(3)

NO.

MIN

MAX

Unit

1

tc(SPC)S

Cycle time, SPICLK(4)

90

ns

2(5)

tw(SPCH)S

Pulse duration, SPICLK high(clock polarity = 0)

30

ns

tw(SPCL)S

Pulse duration, SPICLK low(clock polarity = 1)

30

3(5)

tw(SPCL)S

Pulse duration, SPICLK low(clock polarity = 0)

30

ns

tw(SPCH)S

Pulse duration, SPICLK high(clock polarity = 1)

30

4(5)

td(SPCH-SOMI)S

Delay time, SPISOMI valid after SPICLK high

trf(SOMI) + 15

ns

(clock polarity = 0)

td(SPCL-SOMI)S

Delay time, SPISOMI valid after SPICLK low (clock

trf(SOMI) + 15

polarity = 1)

5(5)

tV(SPCH-SOMI)S

Valid time, SPISOMI data valid after SPICLK high

0

ns

(clock polarity =0)

tV(SPCL-SOMI)S

Valid time, SPISOMI data valid after SPICLK low

0

(clock polarity =1)

6(5)

tsu(SIMO-SPCL)S

Setup time, SPISIMO before SPICLK low(clock

4

ns

polarity = 0)

tsu(SIMO-SPCH)S

Setup time, SPISIMO before SPICLK high(clock

4

polarity = 1)

7(5)

th(SPCL-SIMO)S

Hold time, SPISIMO data valid after SPICLK low

6

ns

(clock polarity = 0)

th(SPCH-SIMO)S

Hold time, SPISIMO data valid after S PICLK high

6

(clock polarity = 1)

8

td(SPCL-SENAH)S

Delay time, SPIENAn high after last SPICLK low

1.5tc(VCLK)

2.5tc(VCLK)+tr(ENAn)+ 26

ns

(clock polarity = 0)

td(SPCH-SENAH)S

Delay time, SPIENAn high after last SPICLK high

1.5tc(VCLK)

2.5tc(VCLK)+tr(ENAn)+ 26

(clock polarity = 1)

9

td(SCSL-SENAL)S

Delay time, SPIENAn low after SPICSn low (if new

tf(ENAn)

tc(VCLK) + tf(ENAn)+ 18

ns

data has been written to the SPI buffer)

(1)

The MASTER bit (SPIGCR1.0) is set and the CLOCK PHASE bit (SPIFMTx.16) is set.

(2)

tc(VCLK) = interface clock cycle time = 1 /f(VCLK)

(3)

For rise and fall timings, see the "switching characteristics for output timings versus load capacitance" table.

(4)

When the SPI is in Slave mode, the following must be true:

tc(SPC)S > 2tc(VCLK) and tc(SPC)S>= 90 ns.

tw(SPCH)S > tc(VCLK) and tw(SPCL)S > tc(VCLK).

(5)

The active edge of the SPICLK signal referenced is controlled by the CLOCK POLARITY bit (SPIFMTx.17).

82

Peripheral and Electrical Specifications

Copyright 2010–2011, Texas Instruments Incorporated

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| TMX320DM642GNZ500 | 64-BIT, 75.19 MHz, OTHER DSP, PBGA548 |

| TN4002PM | 10 MHz - 500 MHz RF/MICROWAVE WIDE BAND LOW POWER AMPLIFIER |

| TN5171PM | 20 MHz - 150 MHz RF/MICROWAVE WIDE BAND MEDIUM POWER AMPLIFIER |

| TOCP172-1MB | 970/1000 um, MULTI MODE, SIMPLEX FIBER OPTIC CONNECTOR |

| TOCP172-20CB | 970/1000 um, MULTI MODE, SIMPLEX FIBER OPTIC CONNECTOR |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| TMS570LS10216SPGE | 制造商:Texas Instruments 功能描述: |

| TMS570LS20206 | 制造商:TI 制造商全稱:Texas Instruments 功能描述:16/32-BIT RISC Flash Microcontroller |

| TMS570LS20206-EP | 制造商:TI 制造商全稱:Texas Instruments 功能描述:TMS570LS Series 16/32-BIT RISC Flash Microcontroller |

| TMS570LS20216 | 制造商:TI 制造商全稱:Texas Instruments 功能描述:16/32-BIT RISC Flash Microcontroller |

| TMS570LS31 | 制造商:TI 制造商全稱:Texas Instruments 功能描述:TMS570LS31 Hercules ARM Safety MCU Development Kit (HDK) |

發(fā)布緊急采購,3分鐘左右您將得到回復。