- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄385942 > TNET3001 (Texas Instruments, Inc.) SONET STS-1 Overhead Terminator(SONET STS-1附加終端) PDF資料下載

參數(shù)資料

| 型號: | TNET3001 |

| 廠商: | Texas Instruments, Inc. |

| 英文描述: | SONET STS-1 Overhead Terminator(SONET STS-1附加終端) |

| 中文描述: | SONET的STS - 1的開銷終結(jié)者(SONET的STS - 1的附加終端) |

| 文件頁數(shù): | 32/49頁 |

| 文件大小: | 1090K |

| 代理商: | TNET3001 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁當(dāng)前第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁

TNETS3001

SONET STS-1 OVERHEAD TERMINATOR

SDNS007B – OCTOBER 1993 – REVISED JUNE 1995

32

POST OFFICE BOX 655303

DALLAS, TEXAS 75265

PRINCIPLES OF OPERATION

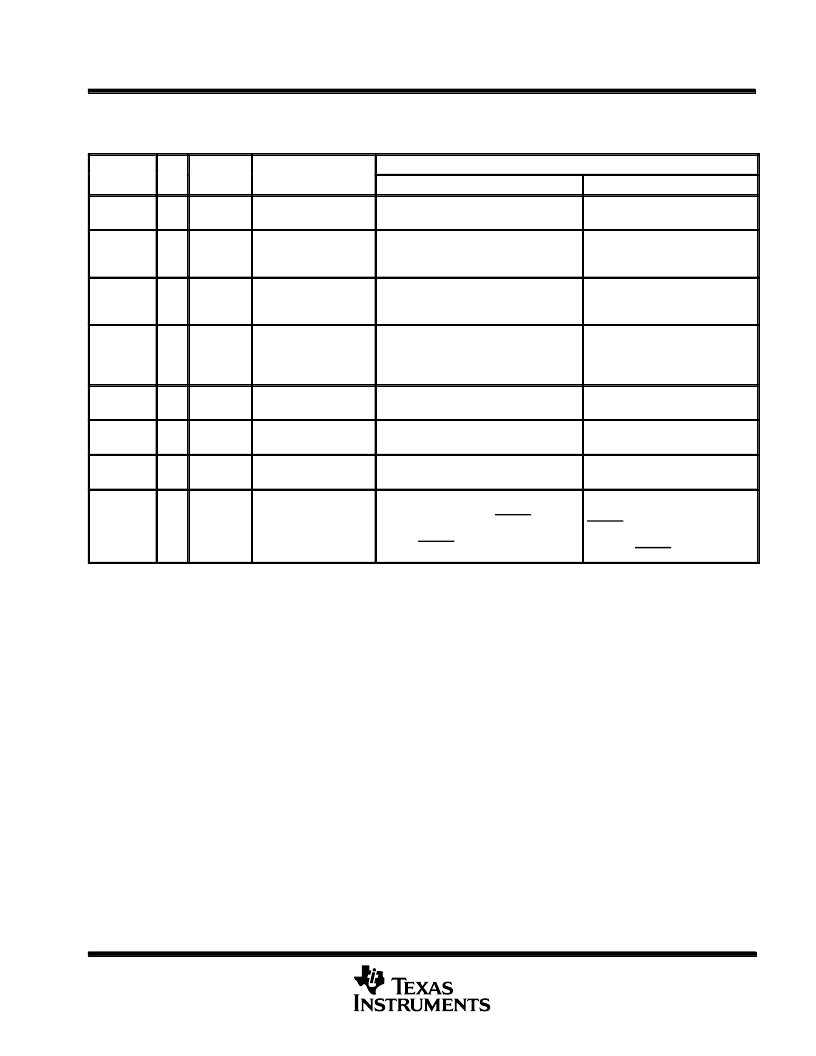

status register 0 (see Notes 19, 20, and 21)

0F0, 0F1,

0F4

BIT

7

SYMBOL

RLOC

NAME

Receive loss of clock

200 ns of no transitions in receive-line

clock RLCI

BIT

SYMBOL

NAME

Any transition of the receive-line

clock RLCI

0F0, 0F1

6

RNPTR

Receive new pointer

A new-pointer value due to new-data flag

or three consecutive frames of different

pointer values

Microprocessor read from address

0F0 or writing 1 to bit 6 of address

0F2

0F0, 0F1,

0F4

5

RPAIS

Receive path AIS

Three consecutive frames of all ones in

H1 and H2 bytes

NDF with valid pointer or three

successive frames with valid

pointer

0F0, 0F1,

0F4

4

RLAIS

Receive line AIS

Five consecutive frames of 111 in the bits

2,1,0 (6,7,8 transmission-bit standard) of

the K2 byte

Five consecutive frames of

patterns other than 111 in the

bits 2,1,0 (6,7,8 transmission-bit

standard) of the K2 byte

0F0, 0F1,

0F4

3

RLOP

Receive loss of pointer

Eight consecutive frames of invalid

pointer or NDF

Three consecutive frames of valid

pointer

0F0, 0F1,

0F4

2

RLOF

Receive loss of frame

Eight consecutive frames of out-of-frame

condition

Eight consecutive frames of

in-frame condition

0F0, 0F1,

0F4

1

ROOF

Receive out of frame

Failure to acquire valid framing pattern

for four consecutive frames

Valid framing pattern exactly 6480

bits apart

0F0, 0F1,

0F4

0

RLOS

Receive loss of signal

STS-1 mode. 20

μ

s of all zeros in the

scrambled data RLDI or RXLOS low.

STS-N mode. 6480 bits of all zeros or all

ones or RXLOS low.

STS-1 mode. A valid framing

pattern in the scrambled data and

RXLOS high.

STS-N mode. Any transition in

RLDI and RXLOS high.

NOTES: 19. The address 0F0 contains latched values of these status bits, which reset on read.

20. The address 0F1 contains latched values of these status bits, but do not reset on read. Write one to an individual bit to reset. Write

back read value to reset the entire register.

21. The address 0F4 contains unlatched values of these status bits. The information is transient.

P

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| TNETA1530 | 155.52-MHz Clock-Generation Device(155.52-MHz時鐘發(fā)生裝置) |

| TNETA1531 | 155.52-MHz Clock-Generation Device(155.52-MHz時鐘發(fā)生裝置) |

| TNETA1545 | Dual Differential PSEUDO-ECL to ECL Transistors and Dual Differential ECL to PSEUDO-ECL Transistors(雙差分ECL TO PSEUDO-ECL轉(zhuǎn)換器和ECL-PSEUDO TO ECL轉(zhuǎn)換器) |

| TNETA1555 | 155.52-Mbit/S Clock-Recovery Device(155.52-MBIT/S時鐘恢復(fù)裝置) |

| TNETA1556 | 155.52-Mbit/S Clock-Recovery Device(155.52-MBIT/S時鐘恢復(fù)裝置) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| TNETA1500A | 制造商:TI 制造商全稱:Texas Instruments 功能描述:155.52-MBIT/S SONET/SDH ATM RECEIVER/TRANSMITTER |

| TNETA1500APCM | 制造商:Texas Instruments 功能描述:TRANSCEIVER, 144 Pin Plastic QFP |

| TNETA1500APGE | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| TNETA1500PCM | 制造商:TI 制造商全稱:Texas Instruments 功能描述:155.52-MBIT/S SONET/SDH ATM RECEIVER/TRANSMITTER |

| TNETA1530DW | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Miscellaneous Clock Generator |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。