- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄366034 > TTRN0110G ATM MULTIPLEXER|BGA|198PIN|CERAMIC PDF資料下載

參數(shù)資料

| 型號: | TTRN0110G |

| 英文描述: | ATM MULTIPLEXER|BGA|198PIN|CERAMIC |

| 中文描述: | ATM多路復(fù)用器|的BGA | 198PIN |陶瓷 |

| 文件頁數(shù): | 7/30頁 |

| 文件大小: | 578K |

| 代理商: | TTRN0110G |

第1頁第2頁第3頁第4頁第5頁第6頁當前第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁

Agere Systems Inc.

7

Data Sheet

March 29, 2002

10 Gbits/s Clock Synthesizer, 16:1 Data Multiplexer

TTRN0110G

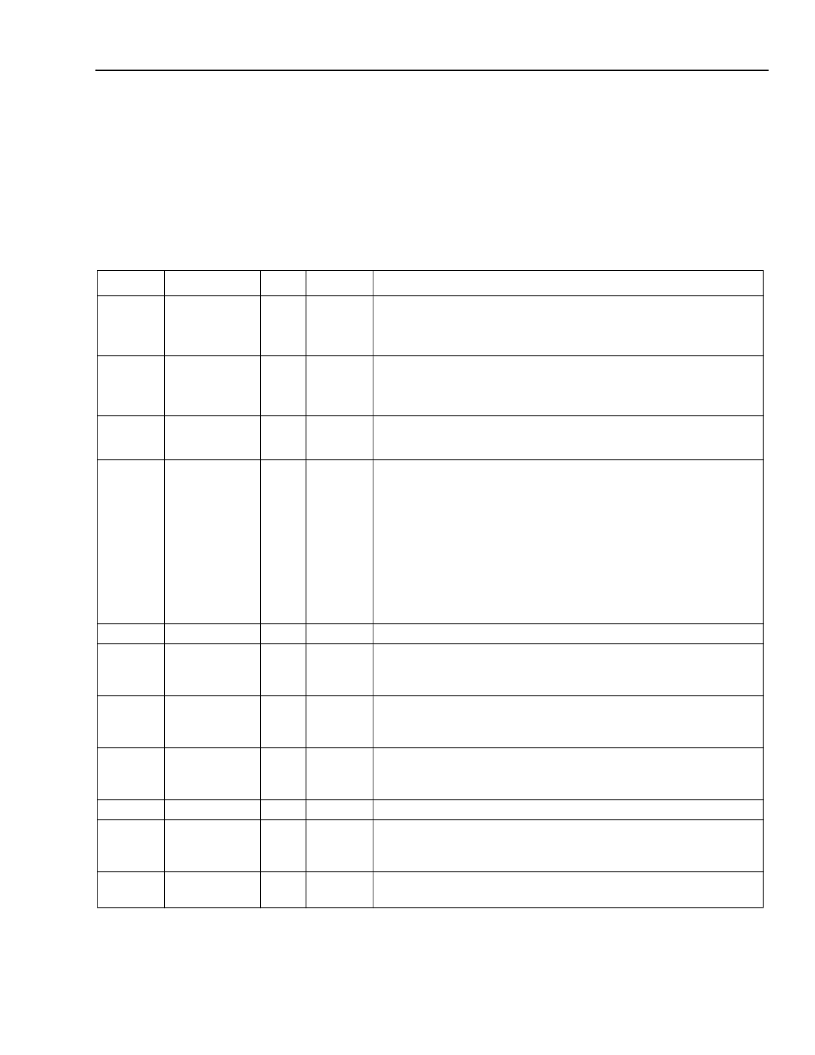

Ball Information

(continued)

Ball Description

Note:

In Table 2, when operating the TTRN0110G device at the OC-192/STM-64 rate, 10 Gbits/s should be

interpreted as 9.9532 Gbits/s. When operating the TTRN0110G device at the Ethernet rate, 10 Gbits/s

should be interpreted as 10.3125 Gbits/s. When operating the TTRN0110G device at RS FEC OC-192/

STM64 rates, 10 Gbits/s should be interpreted as 10.6642 Gbits/s or 10.7092 Gbits/s.

Table 2. Ball Descriptions—10 Gbits/s and Related Signals

Ball

Symbol

*

* Differential pairs are indicated by P and N suffixes. For nondifferential pins, N at the end of the symbol name designates active-low.

I = input, O = output. I

u

indicates an internal pull-up resistor on this pin. I

d

indicates an internal pull-down resistor on this pin. I

t

= an

internal termination resistance of 50

to V

CCD

on this pin.

Type

Level

Name/Description

A11

A9

D10GP

D10GN

O

CML

Data Output (10 Gbits/s NRZ).

10 Gbits/s differential data

output.

Note:

This data rate will scale when operating at different rates.

Loopback Data Output.

Additional 10 Gbits/s differential data

output for system loopback.

D1

F1

LBDP

LBDN

O

CML

Note:

This data rate will scale when operating at different rates.

Clock Output (10 GHz).

10 GHz differential clock output.

A7

A5

CK10GP

CK10GN

O

CML

Note:

This clock rate will scale when operating at different rates.

FEC Rate (Active-Low).

Selects between two operating rate

ranges within the OC-192/STM-64 rate of 9.9532 GHz and the

FEC rate of 10.7092 GHz.

K14

FECN

I

u

0 = Will extend the operating range out to the FEC rate of

10.7092 GHz.

1 or no connection = OC-192/STM-64 rate of 9.9532 GHz to the

Ethernet rate of 10.3 GHz.

Note:

All input and output SONET/SDH clock and data rates will

scale when operating at different rates.

Resistor Reference CML.

CML current bias reference resistor.

Enable CK10GP/N Clock Output.

0 = CK10GP/N buffer powered off.

1 or no connection = CK10GP/N buffer enabled.

Enable LBDP/N Data Output (Active-Low).

0 = LBDP/N buffer enabled.

1 or no connection = LBDP/N buffer powered off.

Invert D10G Data Output (Active-Low).

0 = Invert.

1 or no connection = Noninvert.

Test Clock Input.

(Buffer is powered down when TESTN = 1.)

Select Test Clock (Active-Low).

0 = Select test clock.

1 or no connection = Select VCO.

Resistor Reference VCO.

VCO bias reference resistor. Connect

an 806 k

resistor to V

CCD

.

D8

F9

RREFCML

ENCK10G

I

Analog

CMOS

I

u

F7

ENLBDN

I

u

CMOS

E7

INVDATN

I

u

CMOS

C15

E9

TSTCKP

TESTN

I

t

I

u

CML

CMOS

F14

RREFVCO

I

Analog

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| TTSAL | Crystal Oscillator |

| TU0425W-20 | TUBING 4MM WHITE 20M |

| TCU0425B-1 | Transient Voltage Suppressor Diodes |

| TCU0425B-2 | Transient Voltage Suppressor Diodes |

| TCU0425B-3 | Transient Voltage Suppressor Diodes |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| TTRN012G5 | 制造商:AGERE 制造商全稱:AGERE 功能描述:TTRN012G5 (2.5 Gbits/s) and TTRN012G7 (2.5 Gbits/s and 2.7 Gbits/s) Clock Synthesizer, 16:1 Data Multiplexer |

| TTRN012G53XE1 | 制造商:AGERE 制造商全稱:AGERE 功能描述:TTRN012G5 (2.5 Gbits/s) and TTRN012G7 (2.5 Gbits/s and 2.7 Gbits/s) Clock Synthesizer, 16:1 Data Multiplexer |

| TTRN012G7 | 制造商:AGERE 制造商全稱:AGERE 功能描述:TTRN012G5 (2.5 Gbits/s) and TTRN012G7 (2.5 Gbits/s and 2.7 Gbits/s) Clock Synthesizer, 16:1 Data Multiplexer |

| TTRN012G73XE1 | 制造商:AGERE 制造商全稱:AGERE 功能描述:TTRN012G5 (2.5 Gbits/s) and TTRN012G7 (2.5 Gbits/s and 2.7 Gbits/s) Clock Synthesizer, 16:1 Data Multiplexer |

| TTR-RED | 功能描述:打印機 Ribbon, Resin, 4.33" W x 299’ L, for use RoHS:否 制造商:Seiko Instruments 產(chǎn)品:Printer 電源電壓: 每行點數(shù):9 x 320 打印速度:52.5 cps, 80 cps 紙張寬度:112 mm |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。