- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄359412 > VPX3214 (Electronic Theatre Controls, Inc.) Video Pixel Decoders PDF資料下載

參數(shù)資料

| 型號: | VPX3214 |

| 廠商: | Electronic Theatre Controls, Inc. |

| 英文描述: | Video Pixel Decoders |

| 中文描述: | 視頻解碼器像素 |

| 文件頁數(shù): | 41/80頁 |

| 文件大小: | 752K |

| 代理商: | VPX3214 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁當(dāng)前第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁

PRELIMINARY DATA SHEET

VPX 3220 A, VPX 216 B, VPX 3214 C

MICRONAS INTERMETALL

41

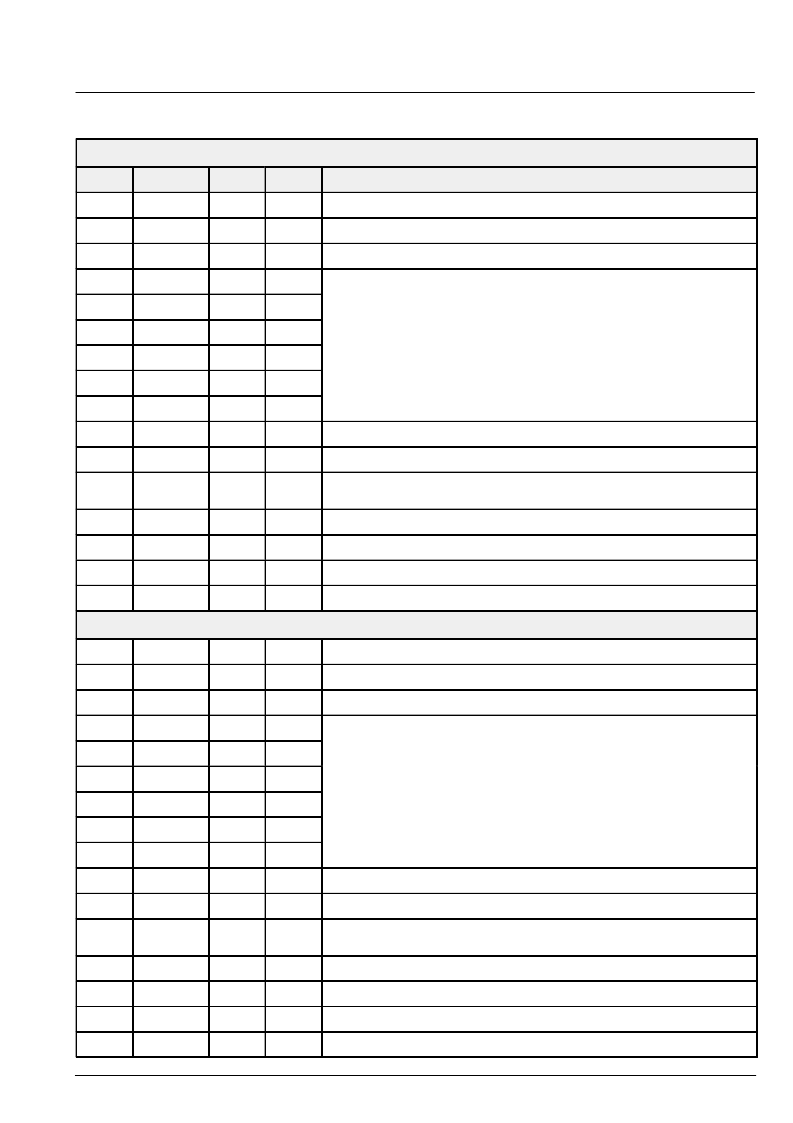

4.9. Initial Values on Reset

PIXCLK LOW on Reset

Table of Initial Values

Type

Name

Address

Data

Description

I

2

C

OFIFO

F0

0A

Half full level to 0A

hex

(10

dec

), bus shuffler off

I

2

C

AFEND

33

0D

Video input 2, chroma ADC from Chroma input, clamp off for chroma ADC

I

2

C

IFC

20

03

IF compensation 0 dB/oct

I

2

C

YMAX

E0

FF

Open up all comparators, so that Alpha Key is always true (set)

I

2

C

YMIN

E1

00

I

2

C

UMAX

E2

7F

I

2

C

UMIN

E3

80

I

2

C

VMAX

E4

7F

I

2

C

VMIN

E5

80

I

2

C

CBM_BRI

E6

00

Brightness to 0

I

2

C

CBM_CON

E7

20

Contrast to 1.0, noise shaping 9 to 8 bit via 1 bit rounding

I

2

C

FORMAT

E8

F8

YUV 422, C

r

,C

b

in binary offset, con/bri clamp to 16

dec

, Gamma dither enabled, Alpha

active low, Alpha median filter enabled

I

2

C

OMUX

F1

00

single clock, PIXCLK input, posedge triggered,

HLEN counter disabled

I

2

C

DRIVER_A

F8

12

Port A, PIXCLK, HF# and FE# strength to 2

I

2

C

DRIVER_B

F9

24

Port B, HREF, VREF, PREF and ALPHA strength to 4

I

2

C

OENA

F2

00

All outputs disabled

PIXCLK HIGH on Reset

I

2

C

OFIFO

F0

0B

Half full level to 0B

hex

(11

dec

), bus shuffler off

I

2

C

AFEND

33

0D

Video input 2, chroma ADC from Chroma input, clamp off for chroma ADC

I

2

C

IFC

20

03

IF compensation 0 dB/oct

I

2

C

YMAX

E0

FF

Open up all comparators, so that Alpha Key is always true (set)

I

2

C

YMIN

E1

00

I

2

C

UMAX

E2

7F

I

2

C

UMIN

E3

80

I

2

C

VMAX

E4

7F

I

2

C

VMIN

E5

80

I

2

C

CBM_BRI

E6

00

Brightness to 0

I

2

C

CBM_CON

E7

20

Contrast to 1.0, noise shaping 9- to 8-bit via 1-bit rounding

I

2

C

FORMAT

E8

F8

YUV 422, C

r

,C

b

in binary offset, con/bri clamp to 16

dec

, Gamma dither enabled, Alpha

active low, Alpha median filter enabled

I

2

C

OMUX

F1

08

single clock, PIXCLK output,

HLEN counter disabled

I

2

C

DRIVER_A

F8

12

Port A, PIXCLK, HF# and FE# strength to 2

I

2

C

DRIVER_B

F9

24

Port B, HREF, VREF, PREF and ALPHA strength to 4

I

2

C

OENA

F2

5F

All outputs enabled: synchronize HREF, VREF with PIXCLK

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| VPX3214C | Video Pixel Decoders |

| VPX3224D | Video Pixel Decoders |

| VPX3224E | Video Pixel Decoders |

| VPX322XE | Video Pixel Decoders |

| VQ1000J | N-Channel Enhancement-Mode MOSFET Transistor(最小漏源擊穿電壓60V,夾斷電流0.225A的N溝道增強型MOSFET晶體管) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| VPX3214C | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Video Pixel Decoders |

| VPX3214C(PLCC44) | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Color Decoder Circuit |

| VPX3214C(QFP44) | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Color Decoder Circuit |

| VPX3216B | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Video Pixel Decoders |

| VPX3216B(PLCC44) | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Color Decoder Circuit |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。