- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄359412 > VPX322XE (MICRONAS SEMICONDUCTOR HOLDING AG) Video Pixel Decoders PDF資料下載

參數(shù)資料

| 型號(hào): | VPX322XE |

| 廠商: | MICRONAS SEMICONDUCTOR HOLDING AG |

| 英文描述: | Video Pixel Decoders |

| 中文描述: | 視頻解碼器像素 |

| 文件頁(yè)數(shù): | 35/92頁(yè) |

| 文件大小: | 567K |

| 代理商: | VPX322XE |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)當(dāng)前第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)

ADVANCE INFORMATION

VPX 322xE

35

Micronas

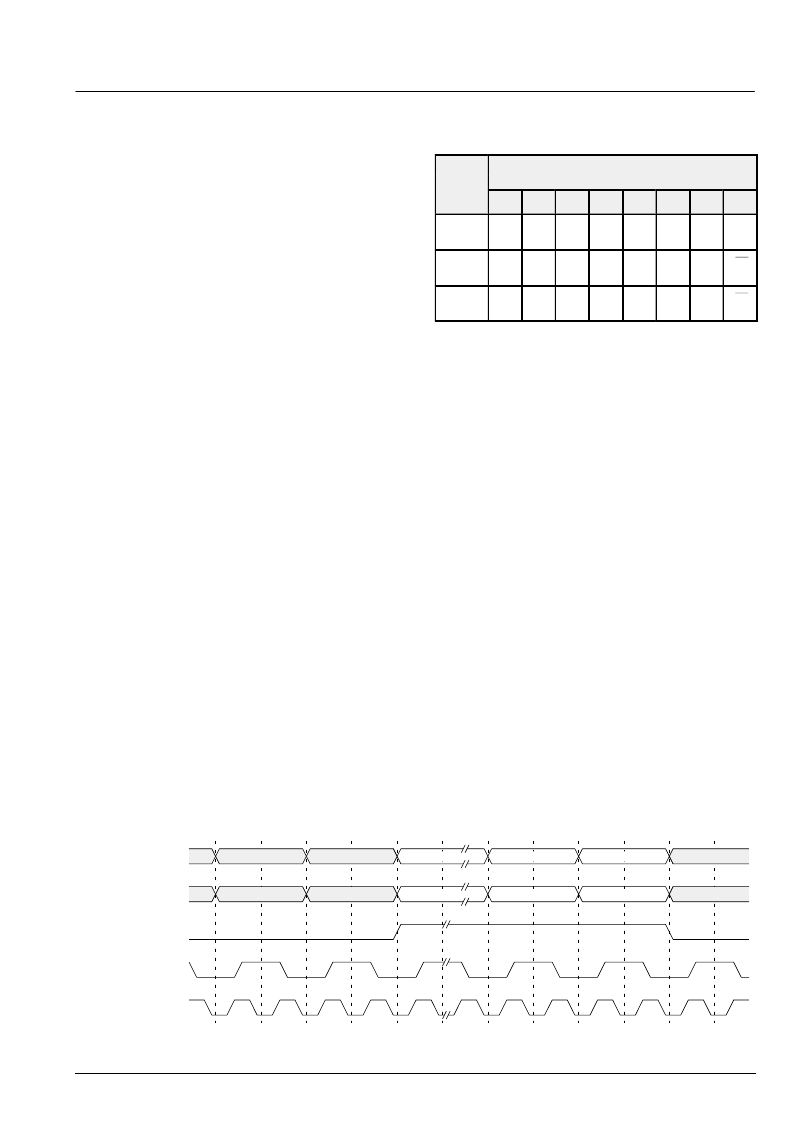

2.14.2. Sliced VBI Data

The sliced data mode is enabled with bit[1] of FP-RAM

0x138 (vbimode). This mode uses the integrated data

slicer and delivers decoded data samples to the output

ports.

The data slicer provides data packets of a constant size

(filled with dummy bytes). The data packets have a de-

fault size of 64 bytes. To reduce the data rate for text sys-

tems with a smaller number of data bytes, the packet

size can be reduced via FP-RAM 0x139.

During lines within the VBI-window, specified by the user

settings in the corresponding Load-Table, the VPX inter-

nally multiplexes the data slicer packets onto the lumi-

nance and chrominance outputs. Since in the 8-bit out-

put modes (ITU-R656, BStream), the values 0, 254 and

255 are protected, each slicer sample is separated into

two nibbles for transmission. Table 2

–

13 shows the im-

plemented data formats.

In each path, one nibble is transmitted twice. The LSB

is inverted for odd parity. This assures that the values 0

and 255 will not occur (for the detection of embedded

syncs). In the mode with embedded timing event codes,

chrominance data will be limited additionally. No signifi-

cant information will be lost since only bit[0] and bit[1] will

be modified. Figure 2

–

39 shows the timing of data and

reference signals in this mode.

Table 2

–

13:

Splitting of sliced data to luminance and

chrominance output

Bit No.

Word

MSB

LSB

7

6

5

4

3

2

1

0

Slicer

Data

S7

S6

S5

S4

S3

S2

S1

S0

Chroma

Output

S7

S6

S5

S4

S7

S6

S5

S4

Luma

Output

S3

S2

S1

S0

S3

S2

S1

S0

The splitting described above can be disabled by setting

bit[6] in the

‘

format_select

’

register. In this case, the

sliced samples will be transmitted in the luminance path

only. To avoid modification of valid data, the limitation of

luminance data in the 8-bit output modes should be sup-

pressed with bit[8] in the same register (note that lumi-

nance codes will not be protected).

Chrominance

(Port B)

VACT

LLC

D

1 (MSBs)

D

63 (MSBs)

D

64 (MSBs)

Luminance

(Port A)

D

1 (LSBs)

D

63 (LSBs)

D

64 (LSBs)

PIXCLK

Fig. 2

–

39:

Timing during lines with sliced VBI-data (single clock mode)

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| VQ1000J | N-Channel Enhancement-Mode MOSFET Transistor(最小漏源擊穿電壓60V,夾斷電流0.225A的N溝道增強(qiáng)型MOSFET晶體管) |

| VQ1000J | N-Channel 60-V (D-S) MOSFET |

| VQ1001J | Dual N-Channel 30-V (D-S) MOSFET with Schottky Diode |

| VQ1001J | N-Channel Enhancement-Mode MOSFET Transistor(最小漏源擊穿電壓30V,夾斷電流0.83A的N溝道增強(qiáng)型MOSFET) |

| VQ1004J | N-Channel Enhancement-Mode MOSFET Transistor(最小漏源擊穿電壓60V,夾斷電流0.46A的N溝道增強(qiáng)型MOSFET晶體管) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| VPX3478 | 制造商:CPI 制造商全稱:CPI 功能描述:X-Band Transmitter |

| VPX60-61ZRZ-DA100-XXP1 | 制造商:Carling Technologies 功能描述:V-SERIES ILLUMINATED PLUG - Bulk |

| VPX641U025E1L1C | 制造商:Mallory 功能描述:RL764X025 |

| VPX66-611KR-00000-XWL1 | 制造商:Carling Technologies 功能描述:V-SERIES ILLUMINATED PLUG - Bulk |

| VPX66-611XR-CS1Y3-XXP2 | 制造商:Carling Technologies 功能描述:V-SERIES ILLUMINATED PLUG - Bulk |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。