- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄378217 > 82865GV (Intel Corp.) Intel 865G/865GV Graphics and Memory Controller Hub PDF資料下載

參數(shù)資料

| 型號: | 82865GV |

| 廠商: | Intel Corp. |

| 英文描述: | Intel 865G/865GV Graphics and Memory Controller Hub |

| 中文描述: | 英特爾865G/865GV圖形和內(nèi)存控制器中樞 |

| 文件頁數(shù): | 30/249頁 |

| 文件大?。?/td> | 3540K |

| 代理商: | 82865GV |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁當前第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁第128頁第129頁第130頁第131頁第132頁第133頁第134頁第135頁第136頁第137頁第138頁第139頁第140頁第141頁第142頁第143頁第144頁第145頁第146頁第147頁第148頁第149頁第150頁第151頁第152頁第153頁第154頁第155頁第156頁第157頁第158頁第159頁第160頁第161頁第162頁第163頁第164頁第165頁第166頁第167頁第168頁第169頁第170頁第171頁第172頁第173頁第174頁第175頁第176頁第177頁第178頁第179頁第180頁第181頁第182頁第183頁第184頁第185頁第186頁第187頁第188頁第189頁第190頁第191頁第192頁第193頁第194頁第195頁第196頁第197頁第198頁第199頁第200頁第201頁第202頁第203頁第204頁第205頁第206頁第207頁第208頁第209頁第210頁第211頁第212頁第213頁第214頁第215頁第216頁第217頁第218頁第219頁第220頁第221頁第222頁第223頁第224頁第225頁第226頁第227頁第228頁第229頁第230頁第231頁第232頁第233頁第234頁第235頁第236頁第237頁第238頁第239頁第240頁第241頁第242頁第243頁第244頁第245頁第246頁第247頁第248頁第249頁

Intel

82865G/82865GV GMCH Datasheet

31

Signal Description

2.2.2

DDR SDRAM Channel B

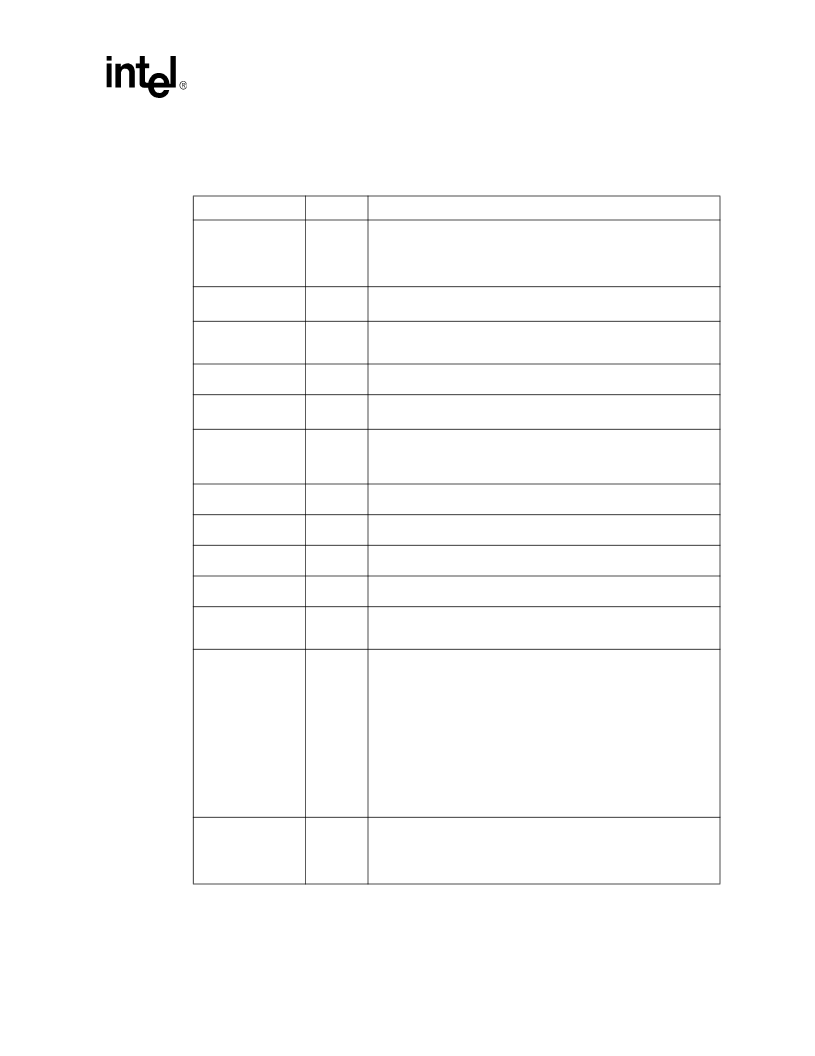

The following DDR signals are for DDR channel B.

Signal Name

Type

Description

SCMDCLK_B[5:0]

O

SSTL_2

Differential DDR Clock

: SCMDCLK_Bx and SCMDCLK_Bx# are

differential clock output pairs. The crossing of the positive edge of

SCMDCLK_Bx and the negative edge of SCMDCLK_Bx# is used to

sample the address and control signals on the SDRAM. There are three

pairs to each DIMM.

SCMDCLK_B[5:0]#

O

SSTL_2

Complementary Differential DDR Clock

: These are the

complementary Differential DDR Clock signals.

SCS_B[3:0]#

O

SSTL_2

Chip Select:

These signals select particular SDRAM components during

the active state. There is one SCS_Bx# for each SDRAM row, toggled on

the positive edge of SCMDCLK_Bx.

SMAA_B[12:0]

O

SSTL_2

Memory Address:

These signals are used to provide the multiplexed

row and column address to the SDRAM.

SMAB_B[5:1]

O

SSTL_2

Memory Address Copies:

These signals are identical to SMAA_B[5:1]

and are used to reduce loading for Selective CPC (clock-per-command).

SBA_B[1:0]

O

SSTL_2

Bank Select (Bank Address):

These signals define which banks are

selected within each SDRAM row. Bank select and memory address

signals combine to address every possible location within an SDRAM

device.

SRAS_B#

O

SSTL_2

Row Address Strobe:

SRAS_B# is used with SCAS_B# and SWE_B#

(along with SCS_B#) to define the SDRAM commands.

SCAS_B#

O

SSTL_2

Column Address Strobe:

SCAS_B# is used with SRAS_B# and

SWE_B# (along with SCS_B#) to define the SDRAM commands.

SWE_B#

O

SSTL_2

Write Enable:

SWE_B# is used with SCAS_B# and SRAS_B# (along

with SCS_B#) to define the SDRAM commands.

SDQ_B[63:0]

I/O

SSTL_2

Data Lines:

SDQ_B signals interface to the SDRAM data bus.

SDM_B[7:0]

O

SSTL_2

Data Mask:

When activated during writes, the corresponding data

groups in the SDRAM are masked. There is one SDM_Bx for every eight

data lines. SDM_Bx can be sampled on both edges of the data strobes.

SDQS_B[7:0]

I/O

SSTL_2

Data Strobes:

Data strobes are used for capturing data. During writes,

SDQS_Bx is centered in data. During reads, SDQS_Bx is edge aligned

with data. The following list matches the data strobe with the data bytes.

Data Strobe

Data Byte

SDQS_B7

SDQ_B[63:56]

SDQS_B6

SDQ_B[55:48]

SDQS_B5

SDQ_B[47:40]

SDQS_B4

SDQ_B[39:32]

SDQS_B3

SDQ_B[31:24]

SDQS_B2

SDQ_B[23:16]

SDQS_B1

SDQ_B[15:8]

SDQS_B0

SDQ_B[7:0]

SCKE_B[3:0]

O

SSTL_2

Clock Enable:

SCKE_B[3:0] are used to initialize DDR SDRAM during

power-up and to place all SDRAM rows into and out of self-refresh

during Suspend-to-RAM. SCKE_B[3:0] are also used to dynamically

power down inactive SDRAM rows. There is one SCKE_Bx per SDRAM

row, toggled on the positive edge of SCMDCLK_Bx.

相關PDF資料 |

PDF描述 |

|---|---|

| 8288 | Bus Controller for SAB 8086 Family Processors |

| 828 | 2 X 2 8-Pole Filters |

| 8291A | GPIB TALKER/LISTENER |

| 829B | SILICON 28V HYPERABRUPT VARACTOR DIODES |

| 829A | SILICON 28V HYPERABRUPT VARACTOR DIODES |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| 82865N | 功能描述:HEX DIE 5/8-11 制造商:apex tool group 系列:* 零件狀態(tài):在售 標準包裝:1 |

| 828661-1 | 功能描述:汽車連接器 25P JUN-TIMER CONN RoHS:否 制造商:Amphenol SINE Systems 產(chǎn)品:Contacts 系列:ATP 位置數(shù)量: 型式:Female 安裝風格: 端接類型: 觸點電鍍:Nickel |

| 828662-1 | 制造商:TE Connectivity 功能描述:CONN TIMER CONN M 16 POS 5MM SLDR ST TH - Bulk 制造商:TE Connectivity 功能描述:16P JUN-TIMER STECK 制造商:TE Connectivity 功能描述:Conn Timer Connector M 16 POS 5mm Solder ST Thru-Hole |

| 82866N | 功能描述:HEX DIE 5/8-18 制造商:apex tool group 系列:* 零件狀態(tài):在售 標準包裝:1 |

| 82867001 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:MOTOR GEARED 12VDC 344RPM |

發(fā)布緊急采購,3分鐘左右您將得到回復。