- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄366891 > CR16HCT5VJE9Y Microcontroller PDF資料下載

參數(shù)資料

| 型號(hào): | CR16HCT5VJE9Y |

| 英文描述: | Microcontroller |

| 中文描述: | 微控制器 |

| 文件頁數(shù): | 82/157頁 |

| 文件大小: | 1256K |

| 代理商: | CR16HCT5VJE9Y |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁當(dāng)前第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁第128頁第129頁第130頁第131頁第132頁第133頁第134頁第135頁第136頁第137頁第138頁第139頁第140頁第141頁第142頁第143頁第144頁第145頁第146頁第147頁第148頁第149頁第150頁第151頁第152頁第153頁第154頁第155頁第156頁第157頁

www.national.com

82

19.3

The ACCESS.bus Interface uses the following registers:

— ACB Serial Data Register (ACBSDA)

— ACB Status Register (ACBST)

— ACB Status Control Register (ACBCST)

— ACB Control 1 Register (ACBCTL1)

— ACB Control 2 Register (ACBCTL2)

— ACB Own Address Register (ACBADDR)

ACB REGISTERS

19.3.1

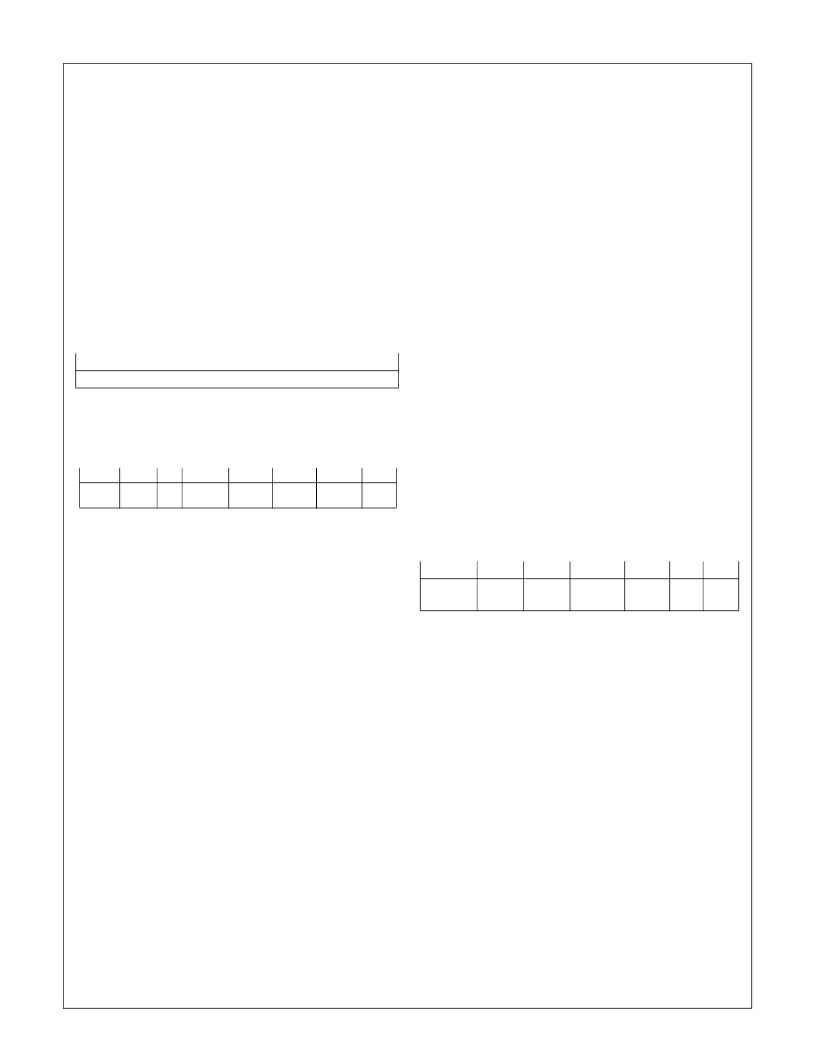

The ACB Serial Data Register (ACBSDA) is a byte-wide,

read/write shift register used to transmit and receive data.

The most significant bit is transmitted (received) first and the

least significant bit is transmitted (received) last. Reading or

writing to the ACBSDA register is allowed when ACB-

ST.SDAST is set; or for repeated starts after setting the

START bit. An attempt to access the register in other cases

produces unpredictable results.

7

DATA

ACB Serial Data Register (ACBSDA)

19.3.2

The ACB Status Register (ACBST) is a byte-wide, read-only

register that maintains current ACB status. Upon reset, and

when the module is disabled, ACBST is cleared (00

16

).

7

6

5

4

SLVST

P

ACB Status Register (ACBST)

XMIT

Direction Bit. The XMIT bit is set when the ACB

module is currently in master/slave transmit

mode. Otherwise it is cleared.

MASTER. When set, the MASTER bit indicates

that the module is currently in master mode. It

is set when a request for bus mastership suc-

ceeds. It is cleared upon arbitration loss (BER

is set) or the recognition of a Stop Condition.

New match. The NMATCH bit is set when the

address byte following a Start Condition, or re-

peated starts, causes a match or a global-call

match. NMATCH is cleared when 1 is written to

it. Writing 0 to NMATCH is ignored. If

ACBCTL1.INTEN is set, an interrupt is sent

when this bit is set.

Stall After Start. The STASTR bit is set by the

successful completion of an address sending

(i.e., a Start Condition sent without a bus error,

or negative acknowledge) if ACBCTL1.STAS-

TRE is set. This bit is ignored in slave mode.

When STASTR is set, it stalls the ACCESS.bus

by pulling down the SCL line, and suspends

any other action on the bus (e.g., receives first

byte in master receive mode). In addition, if

ACBCTL1.INTEN is set, it also sends an inter-

rupt to the core. Writing 1 to STASTR clears it.

It is also cleared when the module is disabled.

Writing 0 to STASTR has no effect.

Negative acknowledge. This bit is set by hard-

ware when a transmission is not acknowledged

on the ninth clock. (In this case SDAST is not

set.) Writing 1 to NEGACK clears it. It is also

MASTER

NMATCH

STASTR

NEGACK

cleared when the module is disabled. Writing 0

to NEGACK is ignored.

Bus Error. BER is set by the hardware when a

Start or Stop Condition is detected during data

transfer (i.e., Start or Stop Condition during the

transfer of bits 2 through 8 and acknowledge

cycle), or when an arbitration problem is de-

tected. Writing 1 to BER clears it. It is also

cleared when the module is disabled. Writing 0

to BER is ignored.

SDA Status. When set, this bit indicates that

the SDA data register is waiting for data (trans-

mit - master or slave) or holds data that should

be read (receive - master or slave). This bit is

cleared when reading from the ACBSDA regis-

ter during a receive, or when written to during a

transmit. When ACBCTL1.START is set, read-

ing ACBSDA register does not clear SDAST.

This enables the ACB to send a repeated start

in master receive mode.

Slave Stop. If set, SLVSTP indicates that a

Stop Condition was detected after a slave

transfer (i.e., after a slave transfer in which

MATCH or GCMATCH is set). Writing 1 to

SLVSTP clears it. It is also cleared when the

module is disabled. Writing 0 to SLVSTP is ig-

nored.

BER

SDAST

SLVSTP

19.3.3

ACB Control Status Register (ACBCST) is a byte-wide, read/

write register that maintains current ACB status. Upon reset

and when the module is disabled, the non-reserved bits of

ACBCST are cleared (0).

7 6

5

4

Reserved TGSCL TSDA

GCMTC

ACB Control Status Register (ACBCST)

BUSY

BUSY. When BUSY is set, it indicates that the

ACB module is:

Generating a Start Condition

In Master mode (ACBST.MASTER is set)

In Slave mode (ACBCST.MATCH or

ACBCST.GCMTCH is set)

In the period between detecting a Start and

completing the reception of the address

byte. After this, the ACB either becomes

not busy or enters slave mode.

The BUSY bit is cleared by the completion of

any of the above states, and by disabling the

module. BUSY is a read only bit. It should al-

ways be written with 0.

Bus Busy When set, BB indicates the bus is

busy. It is set when the bus is active (i.e., a low

level on either SDA or SCL), or by a Start Con-

dition. It is cleared when the module is dis-

abled, upon detection of a Stop Condition, or

when writing 1 to this bit. See “Usage Hints” on

page 84 for a description of the use of this bit.

This bit should be set when either SDA or SCL

are low. This should be done by sampling the

SDA and SCL lines continuously and, setting

the bit if one of them is low. The bit remains set

BB

0

3

2

1

0

SDAST BER NEGACK STASTR

NMATC

H

MASTER

XMIT

3

2

1

BB

0

BUS

Y

H

MATC

H

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| CR16HCT9 | |

| CR16HCT9VJE7 | Microcontroller |

| CR16HCT9VJE7Y | Microcontroller |

| CR16HCT9VJE8 | Microcontroller |

| CR16HCT9VJE8Y | Microcontroller |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| CR16HCT5VJEXY | 制造商:NSC 制造商全稱:National Semiconductor 功能描述:CR16MCT9/CR16MCT5/CR16HCT9/CR16HCT5 16-Bit Reprogrammable/ROM Microcontroller |

| CR16HCT9 | 制造商:NSC 制造商全稱:National Semiconductor 功能描述:CR16MCT9/CR16MCT5/CR16HCT9/CR16HCT5 16-Bit Reprogrammable/ROM Microcontroller |

| CR16HCT9VJE7 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Microcontroller |

| CR16HCT9VJE7Y | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Microcontroller |

| CR16HCT9VJE8 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Microcontroller |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。