- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄298975 > CY7C1512JV18-267BZXC (CYPRESS SEMICONDUCTOR CORP) 4M X 18 QDR SRAM, 0.45 ns, PBGA165 PDF資料下載

參數(shù)資料

| 型號: | CY7C1512JV18-267BZXC |

| 廠商: | CYPRESS SEMICONDUCTOR CORP |

| 元件分類: | SRAM |

| 英文描述: | 4M X 18 QDR SRAM, 0.45 ns, PBGA165 |

| 封裝: | 15 X 17 MM, 1.40 MM HEIGHT, LEAD FREE, MO-216, FBGA-165 |

| 文件頁數(shù): | 26/26頁 |

| 文件大小: | 648K |

| 代理商: | CY7C1512JV18-267BZXC |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁當(dāng)前第26頁

CY7C1510JV18, CY7C1525JV18

CY7C1512JV18, CY7C1514JV18

Document #: 001-14435 Rev. *F

Page 9 of 26

Echo Clocks

Echo clocks are provided on the QDR-II to simplify data capture

on high speed systems. Two echo clocks are generated by the

QDR-II. CQ is referenced with respect to C and CQ is referenced

with respect to C. These are free running clocks and are synchro-

nized to the output clock of the QDR-II. In the single clock mode,

CQ is generated with respect to K and CQ is generated with

respect to K. The timing for the echo clocks is shown in Switching

DLL

These chips use a DLL that is designed to function between

120 MHz and the specified maximum clock frequency. During

power up, when the DOFF is tied HIGH, the DLL is locked after

1024 cycles of stable clock. The DLL is also reset by slowing or

stopping the input clocks K and K for a minimum of 30 ns.

However, it is not necessary to reset the DLL to lock to the

desired frequency. The DLL automatically locks 1024 clock

cycles after a stable clock is presented. Disable the DLL by

applying ground to the DOFF pin. When the DLL is turned off,

the device behaves in QDR-I mode (with one cycle latency and

a longer access time). For information refer to the application

note DLL Considerations in QDRII/DDRII.

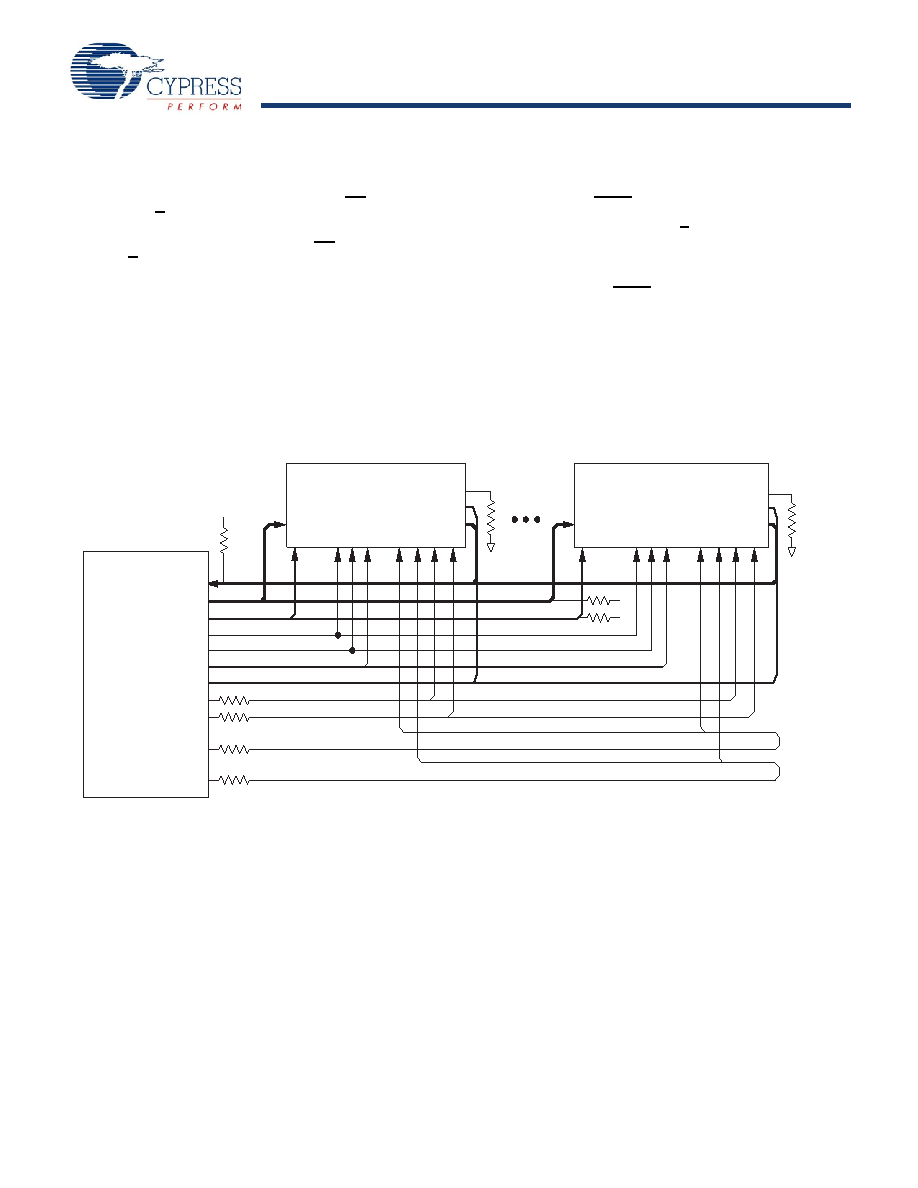

Application Example

Figure 1 shows two QDR-II used in an application.

Figure 1. Application Example

R = 250

ohms

Vt

R

R = 250

ohms

Vt

R

Vt = Vddq/2

R = 50

ohms

R

CC#

D

A

SRAM #2

R

P

S

#

W

P

S

#

B

W

S

#

ZQ

CQ/CQ#

Q

K#

CC#

D

A

K

SRAM #1

R

P

S

#

W

P

S

#

B

W

S

#

ZQ

CQ/CQ#

Q

K#

BUS

MASTER

(CPU

or

ASIC)

DATA IN

DATA OUT

Address

RPS#

WPS#

BWS#

Source K

Source K#

Delayed K

Delayed K#

CLKIN/CLKIN#

K

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| CY7C1515AV18-250BZXI | 2M X 36 QDR SRAM, 0.45 ns, PBGA165 |

| CY7C1522JV18-250BZI | 8M X 8 DDR SRAM, 0.45 ns, PBGA165 |

| CY7C1524KV18-333BZI | 2M X 36 DDR SRAM, 0.45 ns, PBGA165 |

| CY7C1612KV18-333BZXC | 8M X 18 QDR SRAM, PBGA165 |

| CY7C256-45PC | 32K X 8 OTPROM, 45 ns, PDIP28 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| CY7C1512KV18-200BZXC | 功能描述:靜態(tài)隨機存取存儲器 4Mb x 18 200 MHz RoHS:否 制造商:Cypress Semiconductor 存儲容量:16 Mbit 組織:1 M x 16 訪問時間:55 ns 電源電壓-最大:3.6 V 電源電壓-最小:2.2 V 最大工作電流:22 uA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:TSOP-48 封裝:Tray |

| CY7C1512KV18-200BZXI | 制造商:Rochester Electronics LLC 功能描述: 制造商:Cypress Semiconductor 功能描述: |

| CY7C1512KV18-250BZC | 功能描述:靜態(tài)隨機存取存儲器 72MB (4Mx18) 1.8v 250MHz QDR II 靜態(tài)隨機存取存儲器 RoHS:否 制造商:Cypress Semiconductor 存儲容量:16 Mbit 組織:1 M x 16 訪問時間:55 ns 電源電壓-最大:3.6 V 電源電壓-最小:2.2 V 最大工作電流:22 uA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:TSOP-48 封裝:Tray |

| CY7C1512KV18-250BZCT | 功能描述:靜態(tài)隨機存取存儲器 4Mx18 72MB 2.9V RoHS:否 制造商:Cypress Semiconductor 存儲容量:16 Mbit 組織:1 M x 16 訪問時間:55 ns 電源電壓-最大:3.6 V 電源電壓-最小:2.2 V 最大工作電流:22 uA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:TSOP-48 封裝:Tray |

| CY7C1512KV18-250BZI | 功能描述:靜態(tài)隨機存取存儲器 72MB (4Mx18) 1.8v 250MHz QDR II 靜態(tài)隨機存取存儲器 RoHS:否 制造商:Cypress Semiconductor 存儲容量:16 Mbit 組織:1 M x 16 訪問時間:55 ns 電源電壓-最大:3.6 V 電源電壓-最小:2.2 V 最大工作電流:22 uA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:TSOP-48 封裝:Tray |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。