- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄298975 > CY7C1524KV18-333BZI (CYPRESS SEMICONDUCTOR CORP) 2M X 36 DDR SRAM, 0.45 ns, PBGA165 PDF資料下載

參數(shù)資料

| 型號: | CY7C1524KV18-333BZI |

| 廠商: | CYPRESS SEMICONDUCTOR CORP |

| 元件分類: | SRAM |

| 英文描述: | 2M X 36 DDR SRAM, 0.45 ns, PBGA165 |

| 封裝: | 15 X 13 MM, 1.40 MM HEIGHT, MO-216, FBGA-165 |

| 文件頁數(shù): | 17/32頁 |

| 文件大?。?/td> | 883K |

| 代理商: | CY7C1524KV18-333BZI |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁當(dāng)前第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁

CY7C1522KV18, CY7C1529KV18

CY7C1523KV18, CY7C1524KV18

Document Number: 001-00438 Rev. *F

Page 24 of 32

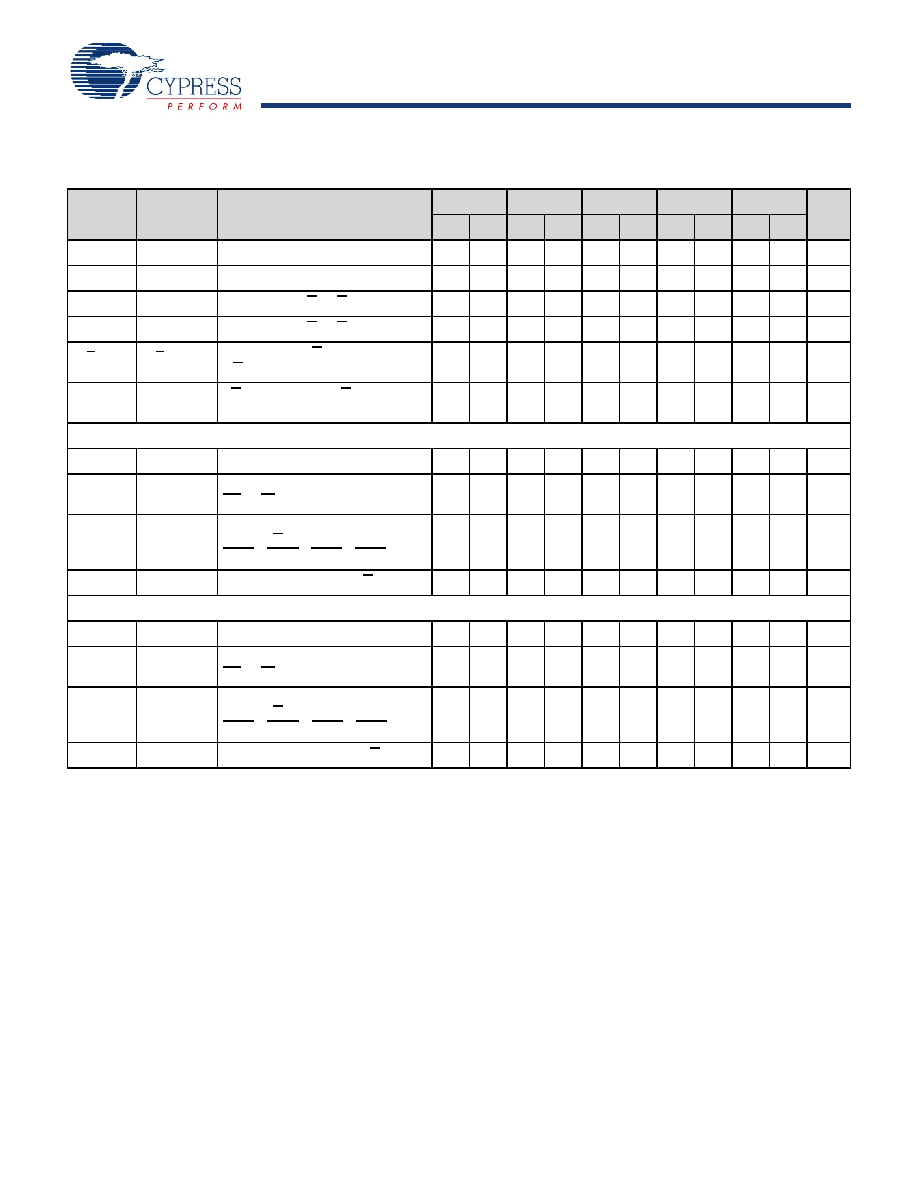

Switching Characteristics

Cypress

Parameter

Consortium

Parameter

Description

333 MHz

300 MHz

250 MHz

200 MHz

167 MHz

Unit

Min Max Min Max Min Max Min Max Min Max

tPOWER

11

ms

tCYC

tKHKH

K Clock and C Clock Cycle Time

3.0

8.4

3.3

8.4

4.0

8.4

5.0

8.4

6.0

8.4

ns

tKH

tKHKL

Input Clock (K/K; C/C) HIGH

1.20

–

1.32

–

1.6

–

2.0

–

2.4

–

ns

tKL

tKLKH

Input Clock (K/K; C/C) LOW

1.20

–

1.32

–

1.6

–

2.0

–

2.4

–

ns

tKHKH

K Clock Rise to K Clock Rise and C

to C Rise (rising edge to rising edge)

1.35

–

1.49

–

1.8

–

2.2

–

2.7

–

ns

tKHCH

K/K Clock Rise to C/C Clock Rise

(rising edge to rising edge)

0

1.30

0

1.45

0

1.802.202.7

ns

Setup Times

tSA

tAVKH

Address Setup to K Clock Rise

0.4

–

0.4

–

0.5

–

0.6

–

0.7

–

ns

tSC

tIVKH

Control Setup to K Clock Rise

(LD, R/W)

0.4

–

0.4

–

0.5

–

0.6

–

0.7

–

ns

tSCDDR

tIVKH

Double Data Rate Control Setup to

Clock (K/K) Rise

(BWS0, BWS1, BWS2, BWS3)

0.3

–

0.3

–

0.35

–

0.4

–

0.5

–

ns

tSD

tDVKH

D[X:0] Setup to Clock (K/K) Rise

0.3

–

0.3

–

0.35

–

0.4

–

0.5

–

ns

Hold Times

tHA

tKHAX

Address Hold after K Clock Rise

0.4

–

0.4

–

0.5

–

0.6

–

0.7

–

ns

tHC

tKHIX

Control Hold after K Clock Rise

(LD, R/W)

0.4

–

0.4

–

0.5

–

0.6

–

0.7

–

ns

tHCDDR

tKHIX

Double Data Rate Control Hold after

Clock (K/K) Rise

(BWS0, BWS1, BWS2, BWS3)

0.3

–

0.3

–

0.35

–

0.4

–

0.5

–

ns

tHD

tKHDX

D[X:0] Hold after Clock (K/K) Rise

0.3

–

0.3

–

0.35

–

0.4

–

0.5

–

ns

Notes

21. When a part with a maximum frequency above 167 MHz is operating at a lower clock frequency, it requires the input timings of the frequency range in which it is operated

and outputs data with the output timings of that frequency range.

22. This part has a voltage regulator internally; tPOWER is the time that the power must be supplied above VDD minimum initially before a read or write operation can be

initiated.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| CY7C1612KV18-333BZXC | 8M X 18 QDR SRAM, PBGA165 |

| CY7C256-45PC | 32K X 8 OTPROM, 45 ns, PDIP28 |

| CY7C2561KV18-450BZC | 8M X 8 QDR SRAM, 0.37 ns, PBGA165 |

| CY7C2566KV18-450BZI | 8M X 8 DDR SRAM, 0.37 ns, PBGA165 |

| CY7C293AL-35WC | 2K X 8 UVPROM, 35 ns, CDIP24 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| CY7C1525JV18250BZC | 制造商:Cypress Semiconductor 功能描述: |

| CY7C1525JV18-250BZC | 功能描述:靜態(tài)隨機存取存儲器 8M x 9 1.8V QDR-II 靜態(tài)隨機存取存儲器 Two-Word Burst RoHS:否 制造商:Cypress Semiconductor 存儲容量:16 Mbit 組織:1 M x 16 訪問時間:55 ns 電源電壓-最大:3.6 V 電源電壓-最小:2.2 V 最大工作電流:22 uA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:TSOP-48 封裝:Tray |

| CY7C1525JV18-250BZCES | 制造商:Rochester Electronics LLC 功能描述: 制造商:Cypress Semiconductor 功能描述: |

| CY7C1525JV18-250BZXC | 功能描述:靜態(tài)隨機存取存儲器 8M x 9 1.8V QDR-II 靜態(tài)隨機存取存儲器 Two-Word Burst RoHS:否 制造商:Cypress Semiconductor 存儲容量:16 Mbit 組織:1 M x 16 訪問時間:55 ns 電源電壓-最大:3.6 V 電源電壓-最小:2.2 V 最大工作電流:22 uA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:TSOP-48 封裝:Tray |

| CY7C1525KV18-250BZC | 功能描述:靜態(tài)隨機存取存儲器 72MB (8Mx9) 1.8v 250MHz QDR II 靜態(tài)隨機存取存儲器 RoHS:否 制造商:Cypress Semiconductor 存儲容量:16 Mbit 組織:1 M x 16 訪問時間:55 ns 電源電壓-最大:3.6 V 電源電壓-最小:2.2 V 最大工作電流:22 uA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:TSOP-48 封裝:Tray |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。