- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄373069 > K4T1G044QQ-HC(L)E6 (SAMSUNG SEMICONDUCTOR CO. LTD.) 1Gb Q-die DDR2 SDRAM Specification PDF資料下載

參數(shù)資料

| 型號: | K4T1G044QQ-HC(L)E6 |

| 廠商: | SAMSUNG SEMICONDUCTOR CO. LTD. |

| 英文描述: | 1Gb Q-die DDR2 SDRAM Specification |

| 中文描述: | 1Gb的調(diào)Q DDR2內(nèi)存芯片規(guī)格 |

| 文件頁數(shù): | 21/44頁 |

| 文件大?。?/td> | 891K |

| 代理商: | K4T1G044QQ-HC(L)E6 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁當(dāng)前第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁

K4T1G084QQ

K4T1G164QQ

Rev. 1.01 November 2007

DDR2 SDRAM

21 of 44

K4T1G044QQ

14.0 General notes, which may apply for all AC parameters

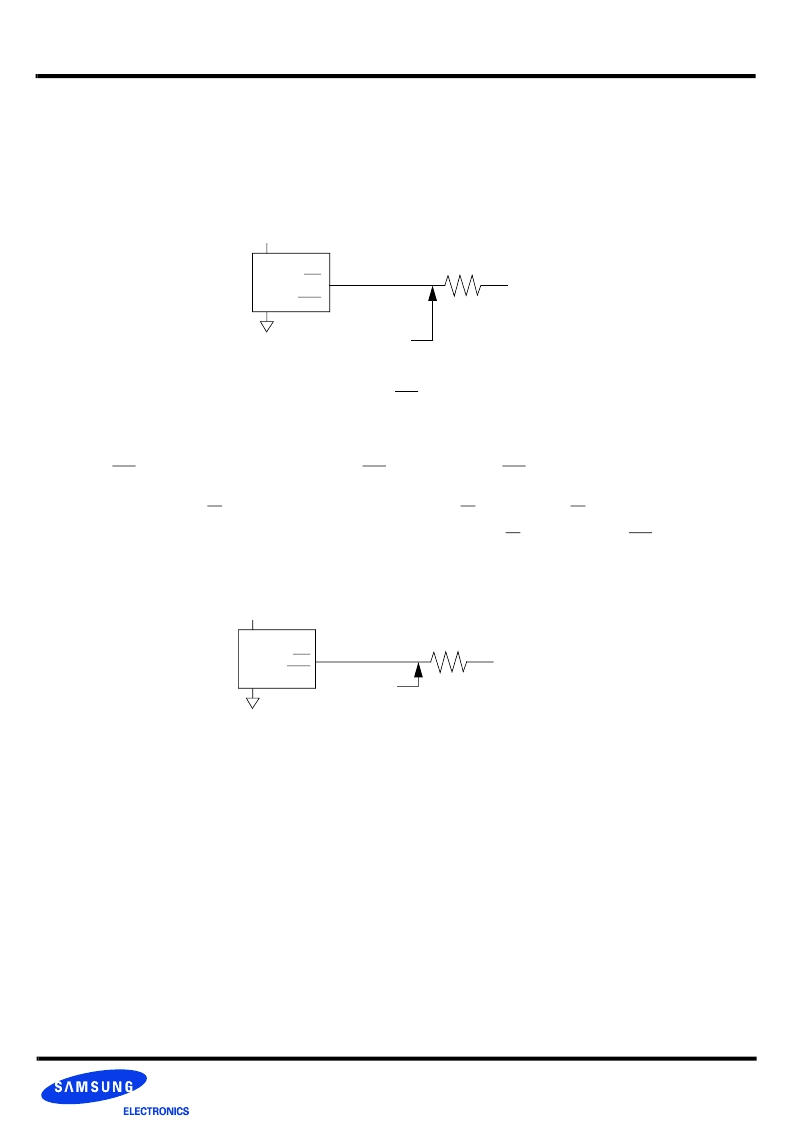

1. DDR2 SDRAM AC timing reference load

Figure 1 represents the timing reference load used in defining the relevant timing parameters of the part. It is not intended to be either a precise repre

sentation of the typical system environment or a depiction of the actual load presented by a production tester. System designers will use IBIS or other

simulation tools to correlate the timing reference load to a system environment. Manufacturers will correlate to their production test conditions (generally

a coaxial transmission line terminated at the tester electronics).

The output timing reference voltage level for single ended signals is the crosspoint with VTT. The output timing reference voltage level for differential

signals is the crosspoint of the true (e.g. DQS) and the complement (e.g. DQS) signal.

2. Slew Rate Measurement Levels

a) Output slew rate for falling and rising edges is measured between VTT - 250 mV and VTT + 250 mV for single ended signals. For differential signals

(e.g. DQS - DQS) output slew rate is measured between DQS - DQS = - 500 mV and DQS - DQS = + 500 mV. Output slew rate is guaranteed by

design, but is not necessarily tested on each device.

b) Input slew rate for single ended signals is measured from Vref(dc) to VIH(ac),min for rising edges and from Vref(dc) to VIL(ac),max for falling edges.

For differential signals (e.g. CK - CK) slew rate for rising edges is measured from CK - CK = - 250 mV to CK - CK = + 500 mV (+ 250 mV to - 500 mV

for falling edges).

c) VID is the magnitude of the difference between the input voltage on CK and the input voltage on CK, or between DQS and DQS for differential strobe.

3. DDR2 SDRAM output slew rate test load

Output slew rate is characterized under the test conditions as shown in Figure 2.

VDDQ

DUT

DQ

DQS

DQS

RDQS

RDQS

Output

V

TT

= V

DDQ

/2

25

Timing

reference

point

Figure 1 - AC Timing Reference Load

VDDQ

DUT

DQ

DQS, DQS

RDQS, RDQS

Output

V

TT

= V

DDQ

/2

25

Test point

Figure 2 - Slew Rate Test Load

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| K4T1G044QQ-HC(L)E7 | 1Gb Q-die DDR2 SDRAM Specification |

| K4T1G044QQ-HC(L)F7 | 1Gb Q-die DDR2 SDRAM Specification |

| K4T1G084QQ | 1Gb Q-die DDR2 SDRAM Specification |

| K4T1G084QQ-HC(L)E6 | 1Gb Q-die DDR2 SDRAM Specification |

| K4T1G084QQ-HC(L)E7 | 1Gb Q-die DDR2 SDRAM Specification |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| K4T1G044QQ-HCLE7 | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:1Gb Q-die DDR2 SDRAM Specification |

| K4T1G044QQ-HCLF7 | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:1Gb Q-die DDR2 SDRAM Specification |

| K4T1G084QAZCD5 | 制造商:Samsung Semiconductor 功能描述: |

| K4T1G084QA-ZCD5 | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:1Gb A-die DDR2 SDRAM Specification |

| K4T1G084QA-ZCE6 | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:1Gb A-die DDR2 SDRAM Specification |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。