- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄377599 > L80227 (LSI CORP) 10BASE-T/100BASE-TX Ethernet Physical Layer Device (PHY)(10BASE-T/100BASE-TX 以太網(wǎng)物理層處理器) PDF資料下載

參數(shù)資料

| 型號: | L80227 |

| 廠商: | LSI CORP |

| 元件分類: | 網(wǎng)絡(luò)接口 |

| 英文描述: | 10BASE-T/100BASE-TX Ethernet Physical Layer Device (PHY)(10BASE-T/100BASE-TX 以太網(wǎng)物理層處理器) |

| 中文描述: | DATACOM, ETHERNET TRANSCEIVER, PQFP64 |

| 封裝: | LQFP-64 |

| 文件頁數(shù): | 94/158頁 |

| 文件大小: | 1084K |

| 代理商: | L80227 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁當(dāng)前第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁第128頁第129頁第130頁第131頁第132頁第133頁第134頁第135頁第136頁第137頁第138頁第139頁第140頁第141頁第142頁第143頁第144頁第145頁第146頁第147頁第148頁第149頁第150頁第151頁第152頁第153頁第154頁第155頁第156頁第157頁第158頁

D

5

M

R

C

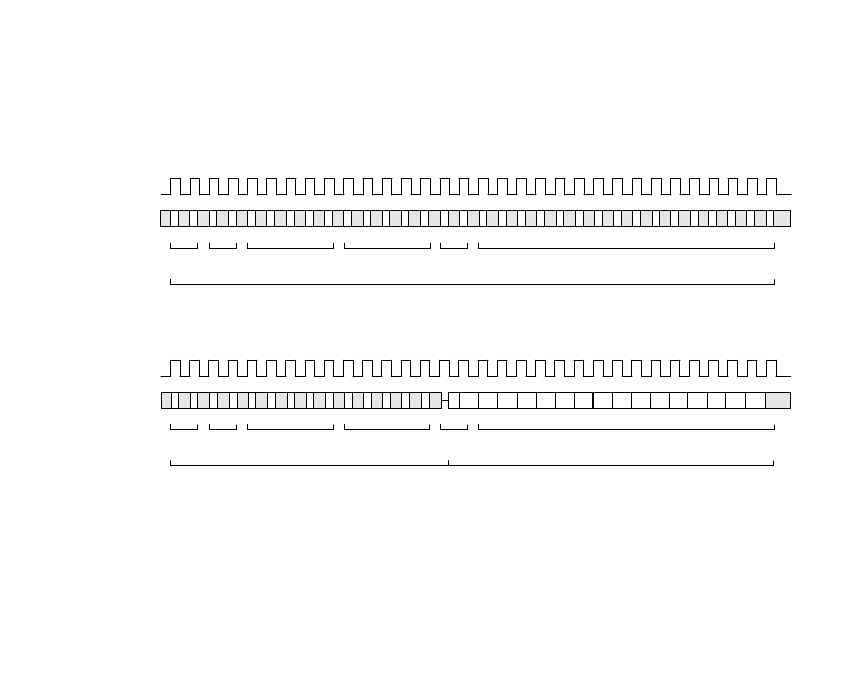

Figure 5.1

MI Serial Port Frame Timing Diagram

WRITE Cycle

MDC

MDIO

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

0

1

0

1

ST

OP

P4

P3

PHYAD

P2

P1

P0

R4

R3

REGAD

R2

R1

R0

1

0

TA

D15 D14 D13 D12 D11

DATA

D10 D9

D8

D7

D6

D5

D4

D3

D2

D1

D0

WRITE Bits

PHY clocks in data on rising edges of MDC with t

s

= 10 ns minimum and t

h

= 10 ns minimum

READ Cycle

MDC

MDIO

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

0

1

1

0

ST

OP

P4

P3

PHYAD

P2

P1

P0

R4

R3

REGAD

R2

R1

R0

Z

0

TA

D15 D14 D13 D12 D11

DATA

D10

D9

D8

D7

D6

D5

D4

D3

D2

D1

D0

WRITE Bits

PHY clocks in data on rising edges of MDC with

t

s

= 10 ns minimum, and t

h

= 10 ns minimum

READ Bits

PHY clocks out data on rising edges of MDC with

t

d

= 20 ns maximum

Note: ST = start bits, OP = operation bits (read or write), PHAD = PHY address, REGAD = register address, TA = turnaround bits

For more detailed information on the timing related to t

s,

t

h, and

t

d,

please see Chapter 6, “Specifications.”

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| L8050HPLT1 | General Purpose Transistors NPN Silicon |

| L8050HPLT1G | General Purpose Transistors NPN Silicon |

| L8050HQLT1 | General Purpose Transistors NPN Silicon |

| L8050HQLT1G | General Purpose Transistors NPN Silicon |

| L8050LT1 | General Purpose Transistors NPN Silicon |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| L80227/B | 制造商:LSI Corporation 功能描述: 制造商:LSI Corporation 功能描述:L80227/B |

| L80227/BI | 制造商:LSI Corporation 功能描述:L80227/BI |

| L80227FR | 制造商:LAUREL ELECTRONICS 功能描述:Laureate 1/8 DIN multi-function counter / timer, universal 85-264 Vac power, two |

| L80227-I | 制造商:LSI Corporation 功能描述:STD CELL ASIC |

| L80227-I-LEADFREE | 制造商:LSI Corporation 功能描述:796000124413 |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。