- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄371014 > MC145225 (Motorola, Inc.) Dual PLL Frequency Synthesizers With DACs and Voltage Multipliers(帶DACs和電壓乘法器的雙PLL頻率合成器) PDF資料下載

參數(shù)資料

| 型號(hào): | MC145225 |

| 廠(chǎng)商: | Motorola, Inc. |

| 英文描述: | Dual PLL Frequency Synthesizers With DACs and Voltage Multipliers(帶DACs和電壓乘法器的雙PLL頻率合成器) |

| 中文描述: | 雙鎖相環(huán)頻率合成器與DAC和電壓倍增器(帶數(shù)模轉(zhuǎn)換器和電壓乘法器的雙鎖相環(huán)頻率合成器) |

| 文件頁(yè)數(shù): | 43/71頁(yè) |

| 文件大小: | 906K |

| 代理商: | MC145225 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)當(dāng)前第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)

MC145225 MC145230

43

MOTOROLA RF/IF DEVICE DATA

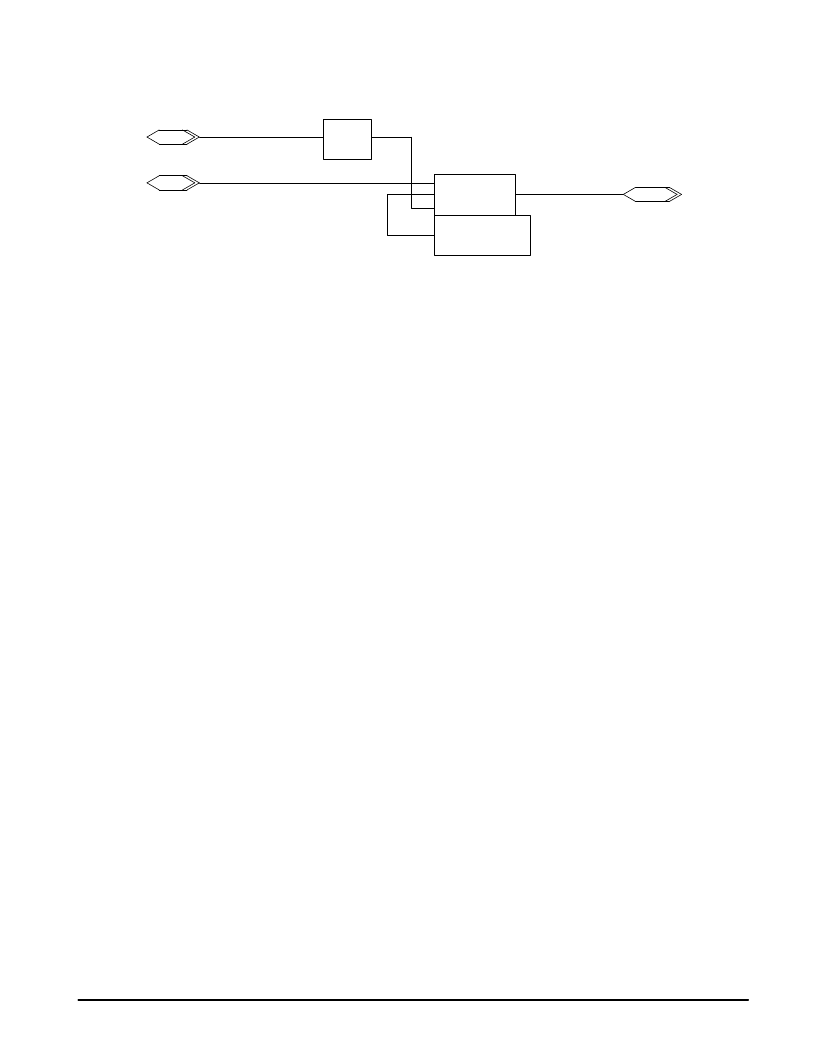

Figure 45. Behavioral RS Flip–flop

If [V(v1)>=1 & V(v2)<1 & V(In2)<1, 5]

If [V(In2)>=1, 0]

If [V(In3)>=1 & V(In2)<1, 5, 0]

Qout

Q

In1

In2

Delay

1 ns

In3

U1

In2

V1

V2

If [V(Q)>=1, 5, 0]

Charge Pump Model

The schematic used for the charge pump in the

phase–frequency detector model is shown in Figure 46. Each

charge pump is made from two analog behavioral blocks.

The blocks chosen are three input behavioral blocks with

current outputs. The two blocks are connected in push–pull

to generate the appropriate source and sink output. The

output of each block is defined using an “If” statement to

monitor the input signals and generate the correct output at

the appropriate time.

One note about this type of design. SPICE does not limit

the output voltage swing necessary to generate the

programmed current. It is possible to implement values for

the loop filter, which will cause the charge pump to exceed

the rail voltage. To limit the output voltage to prevent

exceeding the value of the rails, the two behavioral blocks,

voltage–controlled switches S1 and S2, and constants

VCPHH and VCPHL are added. S1 and S2 on/off resistance

is set to 1

and 1 x 1012

, and the off/on voltage is set to

0 V and 1 V to correspond to the behavioral blocks. The

values defined by the constants are accessible from the

parameter tables on the top level schematic.

VCO Model

The model used for simulating the VCO is shown in

Figure 47. The VCO is composed of a sine wave generator

and a control element. An analog behavioral block is used as

a sine wave generator and a GVALUE element is used as a

control element. The GVALUE is operated as an integrator.

The output of the integrator is defined as

v(int) = k1 v(ctrl) Qc .

The block designated to provide the feedback to the

phase–frequency detector uses a single input analog

behavioral block. The signal shift generated by V1 in the

phase–frequency detector block is used to define the output

frequency of the behavioral block. In this manner, the

switching of the N and R values for the programmable

counters can be simulated. In the implementation shown, the

two frequencies will be either 25 kHz or 100 kHz when locked

to the reference oscillator.

The other behavioral block is used to generate a VCO

output dependent on the loop, but not contributing to the

operation of the loop. This is used to emulate the actual VCO

output with one modification. “H” has been added to the

equation generating the sine wave. If H is defined as 1, the

sine wave generated will be the same as the expected VCO

output. If H is chosen as some value greater than 1, the

frequency of the output will be reduced accordingly. This is

useful when running simulations designed to show reference

spur levels.

In cases where it is desirable to view reference spur levels,

simulation can become difficult or impossible. For example,

consider the circuit that is being discussed. This circuit

represents the evaluation kit (MC145230EVK) using a VCO

tunable between 733 MHz to 742 MHz, with a step frequency

of 25 kHz.

NOTE

This example is for reference only. The

maximum operating frequency of the MC145181

is 550 MHz. Operation of the VCO at

frequencies greater than 550 MHz requires the

inclusion of additional external division such as a

prescaler.

To obtain useful information from the simulation, a

sampling rate greater than the Nyquist limit must be used

(three to five samples per cycle). This dictates a step size

less than 1/2 nanosecond. Additionally, the reference

frequency is only 25 kHz. To accurately represent the

conditions for spur generation, the simulation time must be

long enough to include a sufficient number of fr periods.

Otherwise, no spurs are generated. In addition, the data file

system is limited to 2 Gbyte, either in the NT 4.0 operating

system or in PSpice itself. If the file exceeds 2 Gbyte, the

data is discarded. To simulate reference spur generation at

730 MHz, a 1 ms simulation time was chosen. The simulation

ran for several hours and generated a data file just under

2 Gbyte. The result is shown in Figure 48. The plot obtained

from the EVK is shown in Figure 49 for comparison.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MC145230 | Dual PLL Frequency Synthesizers With DACs and Voltage Multipliers(帶DACs和電壓乘法器的雙PLL頻率合成器) |

| MC14528BCL | Dual Monostable Multivibrator |

| MC14528 | DEFLECTION PROCESSOR FOR MULTISYNC MONITORS |

| MC14528 | Dual Monostable Multivibrator |

| MC14528BFEL | Dual Monostable Multivibrator |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MC14522BCP | 制造商:Motorola Inc 功能描述:Counter, Down, Decade, 16 Pin, Plastic, DIP |

| MC14522BDW | 制造商:Motorola Inc 功能描述: |

| MC14526B AC7 WAF | 制造商:ON Semiconductor 功能描述: |

| MC14526BAC7 WAF | 制造商:ON Semiconductor 功能描述: |

| MC14526BCL | 制造商: 功能描述: 制造商:undefined 功能描述: |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。