- 您現在的位置:買賣IC網 > PDF目錄371014 > MC145225 (Motorola, Inc.) Dual PLL Frequency Synthesizers With DACs and Voltage Multipliers(帶DACs和電壓乘法器的雙PLL頻率合成器) PDF資料下載

參數資料

| 型號: | MC145225 |

| 廠商: | Motorola, Inc. |

| 英文描述: | Dual PLL Frequency Synthesizers With DACs and Voltage Multipliers(帶DACs和電壓乘法器的雙PLL頻率合成器) |

| 中文描述: | 雙鎖相環(huán)頻率合成器與DAC和電壓倍增器(帶數模轉換器和電壓乘法器的雙鎖相環(huán)頻率合成器) |

| 文件頁數: | 53/71頁 |

| 文件大小: | 906K |

| 代理商: | MC145225 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁當前第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁

MC145225 MC145230

53

MOTOROLA RF/IF DEVICE DATA

Figure 57. VCO Behavioral Model

1 x 1099

R1

1 x 106

1 x 10–6

+

Parameters:

tw

fc

K1

6.283

38.756 x 106

21.36283005 x 106

Parameters:

Qc

1 x 10–6

In+

In–

Out+

Out–

evalue

ctrl

In+

In–

gvalue

G1

E1

C1

int

ctrl

Out

IC = 0

time + v(int)

N

fc

sin tw

v(ctrl) Qc

tw N

k1

5 V

0 V

0

G1 performs the operation [k1/(tw N)] v(ctrl) Qc. This

integrates the input ctrl to produce a voltage ramp used by E1

to produce the desired output. This input is integrated by C1

whose value should equal Qc for most applications. R1 is

required by SPICE to prevent a floating node error.

E1 performs the calculations necessary to generate a sine

wave of the desired frequency based on the values listed in

the parameter tables and the value of ctrl. The output of E1 is

multiplied by 1 x 106 and limited to 0 and 5 to obtain a square

wave with a fast rise/fall time. Since I/O_STM is a standard

model whose values are 0 and 5, these are used here and in

the phase detector rather than modifying the component

libraries.

The parameter tables provide a convenient method for

setting VCO parameters. tw is 2

π

, fc is the zero control

voltage VCO frequency, and K1 is the VCO gain in rad/s/V.

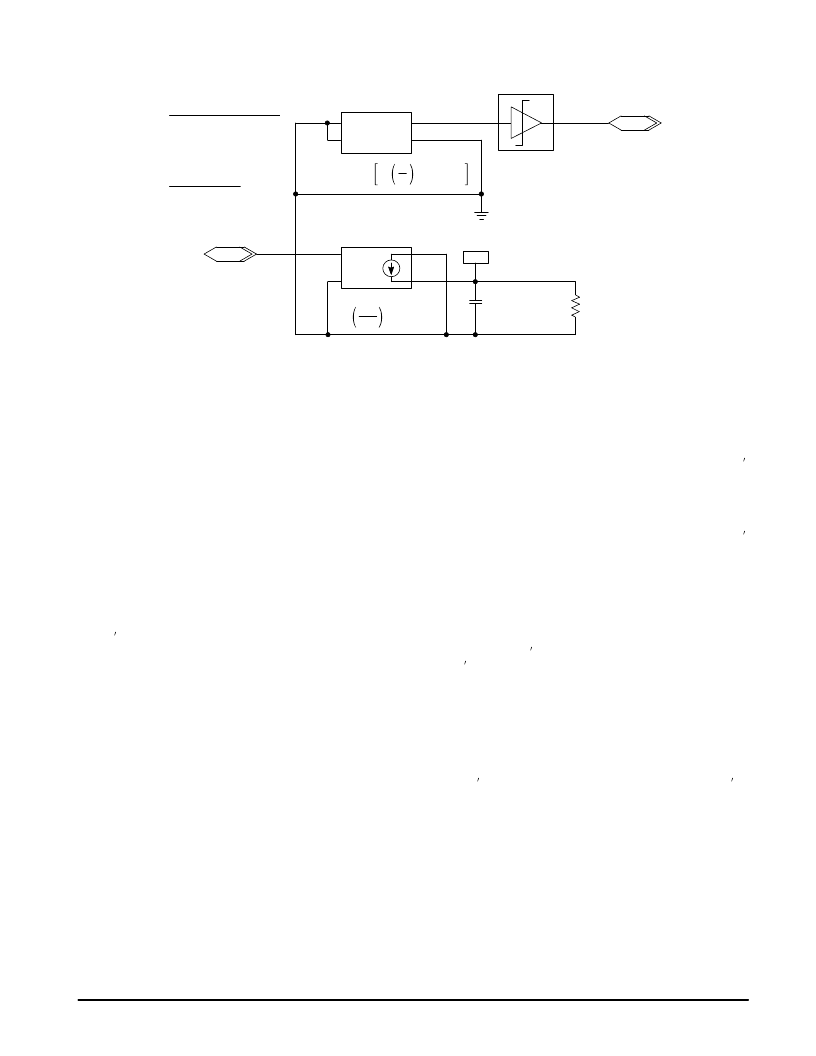

The sub–schematic for the phase/frequency detector

section of the drawing is shown in Figure 58. This is

composed of two blocks, HB3 and HB4. HB3 performs the

PDout function with HB4 performing the actual phase

detector operation.

The circuit for the phase/frequency detector is shown in

Figure 59. The model is made up of two pulse generators,

two RS flip–flops, and appropriate behavioral gates.

HB1 and HB2 are RS flip–flops. These are constructed

from behavioral blocks as shown in Figure 60. A behavioral

AND gate with a 5 ns delay completes the three state (

±

2

π

)

phase/frequency detector. The STP function ensures the RS

flip–flops are reset at initiation.

To perform the phase detector function, the Ref and fin

inputs of the behavioral RS flip–flops are configured to

simulate edge triggered operation. This is achieved by

placing a 1 ns delay in the Ref and fin signal paths. The input

and output of the delay are compared by the input behavioral

block and interpreted as a 1 ns pulse. These pulses are used

to set HB1 and HB2. If fin leads Ref, the In flip–flop, HB2, will

be set first. When Ref leads fin, the Ref flip–flop, HB1, will be

set first. The lagging edge drives the second flip–flop output

high and the behavioral AND gate then resets both flip–flops.

The delay line at the output of the behavioral AND gate

prevents PSpice from being confused and also completes

the simulation of the phase detector. The outputs of the two

RS flip=flops are labeled R

φ

and V

φ

. The time between the

leading and lagging edges is reflected in the pulse width of

the leading edge flip–flop. The lagging edge flip–flop will

display a narrow pulse equal in width to the value chosen for

the delay at the output of the behavioral AND gate. This

should be programmed to the minimum value as specified by

the data sheet and is usually 5 ns or less.

Since the outputs R

φ

and V

φ

are pure logic signals,

additional circuitry is necessary to produce the output PDout.

This output should be high impedance when not driving, and

pull either high or low depending on which function (R

φ

or V

φ

)

is active. The circuitry shown in Figure 61 performs this

function.

To eliminate the need for discrete modeling of PDout,

analog behavioral modeling is used. Analog behavioral

blocks ABMI/2, generate a current source/sink output

whenever the appropriate input is high.

A second set of behavioral blocks monitor the output

idrive, and switch on the appropriate voltage controlled

switch whenever the output rises to the value of VDD (phase

detector supply voltage) or drops to 0.

To model PDout, either a model of the transistors used for

PDout must be used or this behavioral arrangement can be

used. Since the output is specified by a specific output level

and current capability, this arrangement suffices. The output

swing becomes VCPH in the schematic and the current

capability is CP. If a non–zero value is desired for Vlo, the

value VCPL is adjusted from the parameter table on the top

level schematic.

This arrangement allows setting the output voltage swing

of PDout by specifying VCPH, the current drive of PDout by

specifying the desired value for CP, and leakage values can

be simulated by setting the appropriate attributes for S1 and

S4 or by adding additional resistance.

Simulation

Figures 62 and 63 are the simulation results of running a

transient analysis on the example shown above. The time to

lock from power on is simulated by setting the initial condition

(IC1) to 0 and running the simulation. Figure 62 is the time

versus value of the VCO control voltage. Figure 63 shows the

output at the input of the loop filter and can be used to

determine lock time.

相關PDF資料 |

PDF描述 |

|---|---|

| MC145230 | Dual PLL Frequency Synthesizers With DACs and Voltage Multipliers(帶DACs和電壓乘法器的雙PLL頻率合成器) |

| MC14528BCL | Dual Monostable Multivibrator |

| MC14528 | DEFLECTION PROCESSOR FOR MULTISYNC MONITORS |

| MC14528 | Dual Monostable Multivibrator |

| MC14528BFEL | Dual Monostable Multivibrator |

相關代理商/技術參數 |

參數描述 |

|---|---|

| MC14522BCP | 制造商:Motorola Inc 功能描述:Counter, Down, Decade, 16 Pin, Plastic, DIP |

| MC14522BDW | 制造商:Motorola Inc 功能描述: |

| MC14526B AC7 WAF | 制造商:ON Semiconductor 功能描述: |

| MC14526BAC7 WAF | 制造商:ON Semiconductor 功能描述: |

| MC14526BCL | 制造商: 功能描述: 制造商:undefined 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復。