- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄378056 > PM7351-BI (PMC-SIERRA INC) OCTAL SERIAL LINK MULTIPLEXER PDF資料下載

參數(shù)資料

| 型號(hào): | PM7351-BI |

| 廠商: | PMC-SIERRA INC |

| 元件分類: | 數(shù)字傳輸電路 |

| 英文描述: | OCTAL SERIAL LINK MULTIPLEXER |

| 中文描述: | ATM/SONET/SDH SUPPORT CIRCUIT, PBGA304 |

| 封裝: | 31 X 31 MM, 1.51 MM HEIGHT, 1.27 MM PITCH, SBGA-304 |

| 文件頁(yè)數(shù): | 24/174頁(yè) |

| 文件大小: | 1790K |

| 代理商: | PM7351-BI |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)當(dāng)前第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)第94頁(yè)第95頁(yè)第96頁(yè)第97頁(yè)第98頁(yè)第99頁(yè)第100頁(yè)第101頁(yè)第102頁(yè)第103頁(yè)第104頁(yè)第105頁(yè)第106頁(yè)第107頁(yè)第108頁(yè)第109頁(yè)第110頁(yè)第111頁(yè)第112頁(yè)第113頁(yè)第114頁(yè)第115頁(yè)第116頁(yè)第117頁(yè)第118頁(yè)第119頁(yè)第120頁(yè)第121頁(yè)第122頁(yè)第123頁(yè)第124頁(yè)第125頁(yè)第126頁(yè)第127頁(yè)第128頁(yè)第129頁(yè)第130頁(yè)第131頁(yè)第132頁(yè)第133頁(yè)第134頁(yè)第135頁(yè)第136頁(yè)第137頁(yè)第138頁(yè)第139頁(yè)第140頁(yè)第141頁(yè)第142頁(yè)第143頁(yè)第144頁(yè)第145頁(yè)第146頁(yè)第147頁(yè)第148頁(yè)第149頁(yè)第150頁(yè)第151頁(yè)第152頁(yè)第153頁(yè)第154頁(yè)第155頁(yè)第156頁(yè)第157頁(yè)第158頁(yè)第159頁(yè)第160頁(yè)第161頁(yè)第162頁(yè)第163頁(yè)第164頁(yè)第165頁(yè)第166頁(yè)第167頁(yè)第168頁(yè)第169頁(yè)第170頁(yè)第171頁(yè)第172頁(yè)第173頁(yè)第174頁(yè)

RELEASED

PM7351 S/UNI-VORTEX

DATA SHEET

PMC-1980582

ISSUE 5

OCTAL SERIAL LINK MULTIPLEXER

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

14

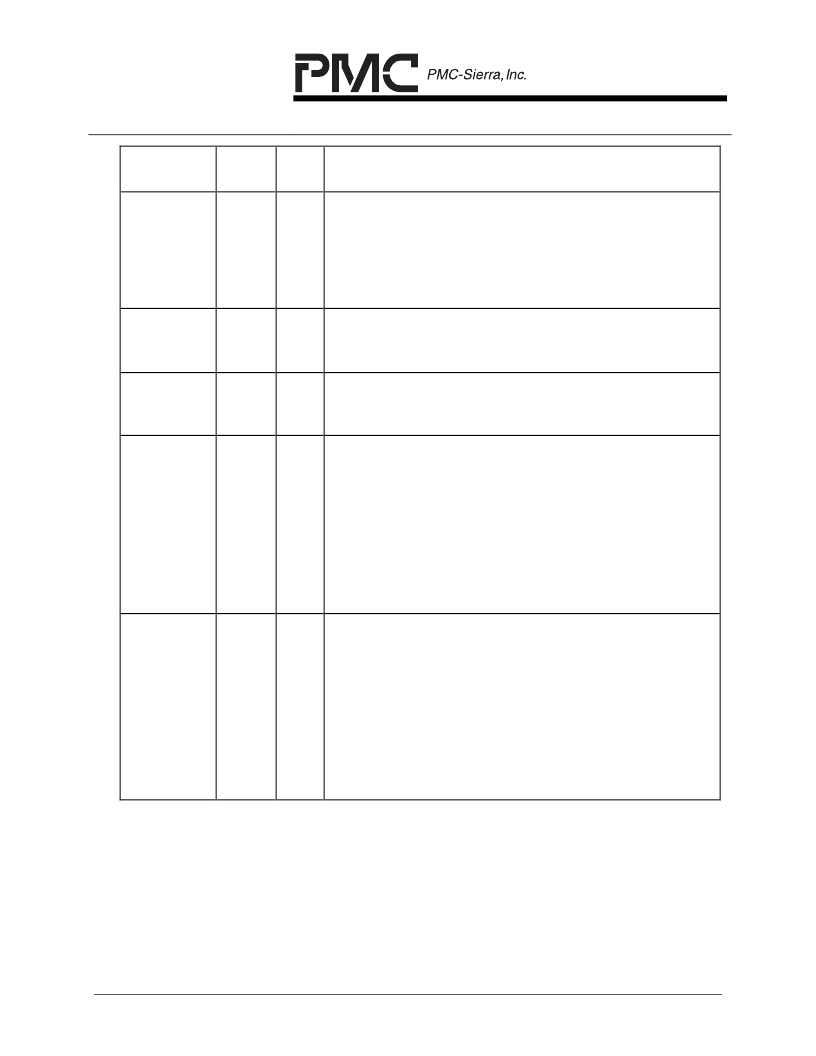

Ball

Name

Type

Ball

No.

Function

REFCLK

Input

AB13 The reference clock input (REFCLK) must provide a

jitter-free reference clock. It is used as the reference

clock by both clock recovery and clock synthesis

circuits. Any jitter below 1 MHz is transferred directly

to the TXDn+/- outputs. The high speed serial

interface bit rate is eight times the REFCLK frequency.

RES

RESK

Analog

P4

P3

A 4.75k

±1% resistor must be connected between

these two balls to achieve the correct LVDS output

signal levels.

ATP0

ATP1

Analog

K3

K4

The Analog Test Points (ATP) are provided for

production test purposes. In mission mode they are

high impedance and should be connected to ground.

TX8K

Input

J23

The transmit 8 kHz timing reference (TX8K) input

allows a traceable signal to be transmitted to the far

end of the high-speed serial links via TXD0+/- through

TXD7+/-. A rising edge on TX8K is encoded in the

next cell transmitted.

Although TX8K is targeted at a typical need of

transporting an 8 kHz signal, its frequency is not

constrained to 8 kHz. Any frequency less than the cell

rate is permissible.

RX8K

Output

A14

The receive 8 kHz timing reference (RX8K) output

presents the timing extracted from one of the receive

high-speed serial links.

The rising edge of RX8K is accurate to the nearest

byte boundary of the high-speed serial link; therefore,

a small amount of jitter is present. At a link rate of

155.52 Mb/s, the jitter is 63ns peak-to-peak.

Pulses on RX8K are always 16 high-speed serial link

bit periods wide (two REFCLK periods).

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| PM7364 | Frame Engine and Datalink Manager |

| PM7364-BI | FRAME ENGINE AND DATA LINK MANAGER |

| PM7366 | FRAME ENGINE AND DATA LINK MANAGER |

| PM7366-BI | TVS BI-DIR 30V 1500W DO-201 |

| PM7366-PI | FRAME ENGINE AND DATA LINK MANAGER |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| PM-736 | 制造商:Eclipse Tools 功能描述: |

| PM7364 | 制造商:PMC 制造商全稱:PMC 功能描述:FRAME ENGINE AND DATA LINK MANAGER |

| PM7364-BI | 制造商:PMC-Sierra 功能描述:PROTOCOL CONTROLLER, 256 Pin, BGA |

| PM7366 | 制造商:PMC 制造商全稱:PMC 功能描述:FRAME ENGINE AND DATA LINK MANAGER |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。