- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄371435 > 28F020 (Intel Corp.) 5 V Bulk Erase Flash Memory(5V 整體擦寫閃速存儲(chǔ)器) PDF資料下載

參數(shù)資料

| 型號(hào): | 28F020 |

| 廠商: | Intel Corp. |

| 英文描述: | 5 V Bulk Erase Flash Memory(5V 整體擦寫閃速存儲(chǔ)器) |

| 中文描述: | 5伏體擦除閃存(5V的整體擦寫閃速存儲(chǔ)器) |

| 文件頁數(shù): | 12/47頁 |

| 文件大小: | 758K |

| 代理商: | 28F020 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁當(dāng)前第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁

28F010/28F020

E

12

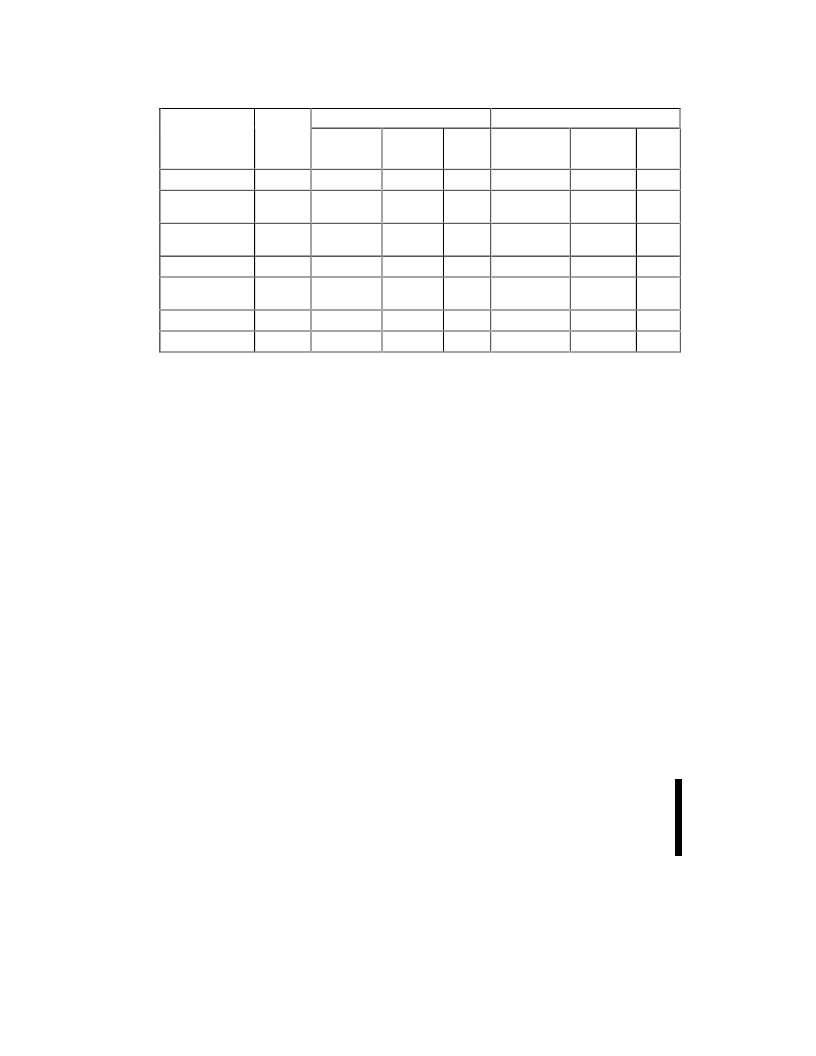

Table 3. Command Definitions

First Bus Cycle

Second Bus Cycle

Command

Bus

Cycles

Req’d

Operation

(1)

Address

(2)

Data

(3)

Operation

(1)

Address

(2)

Data

(3)

Read Memory

1

Write

X

00H

Read Intelligent

Identifier Codes

(4)

3

Write

IA

90H

Read

IA

ID

Set-Up

Erase/Erase

(5)

2

Write

X

20H

Write

X

20H

Erase Verify

(5)

2

Write

EA

A0H

Read

X

EVD

Set-Up Program/

Program

(6)

2

Write

X

40H

Write

PA

PD

Program Verify

(6)

2

Write

X

C0H

Read

X

PVD

Reset

(7)

2

Write

X

FFH

Write

X

FFH

NOTES:

1.

2.

Bus operations are defined in Table 2.

IA = Identifier address: 00H for manufacturer code, 01H for device code.

EA = Erase Address: Address of memory location to be read during erase verify.

PA = Program Address: Address of memory location to be programmed.

Addresses are latched on the falling edge of the WE# pulse.

ID = Identifier Data: Data read from location IA during device identification (Mfr = 89H Device = (B4H for 28F010, BDH for

28F020).

EVD = Erase Verify Data: Data read from location EA during erase verify.

PD = Program Data: Data to be programmed at location PA. Data is latched on the rising edge of WE#.

PVD = Program Verify Data: Data read from location PA during program verify. PA is latched on the Program command.

Following the Read Intelligent ID command, two read operations access manufacturer and device codes.

Figure 5 illustrates the 28F010/28F020 Quick-Erase Algorithmflowchart.

Figure 4 illustrates the 28F010/28F020 Quick-Pulse Programming Algorithmflowchart.

The second bus cycle must be followed by the desired command register write.

3.

4.

5.

6.

7.

2.2.2.1

Read Command

While V

PP

is high, for erasure and programming,

memory contents can be accessed via the Read

command. The read operation is initiated by writing

00H into the command register. Microprocessor

read cycles retrieve array data. The device remains

enabled for reads until the command register

contents are altered.

The default contents of the register upon V

PP

power-up is 00H. This default value ensures that no

spurious alteration of memory contents occurs

during the V

PP

power transition. Where the V

PP

supply is hardwired to the 28F010 or the 28F020,

the device powers-up and remains enabled for

reads until the command register contents are

changed.

Refer to the AC Characteristics

—Read-Only

Operations

and waveforms for specific timing

parameters.

2.2.2.2

Intelligent Identifier Command

Flash memories are intended for use in applications

where the local CPU alters memory contents. As

such, manufacturer and device codes must be

accessible while the device resides in the target

system. PROM programmers typically access

signature codes by raising A

9

to a high voltage.

However, multiplexing high voltage onto address

lines is not a desired system design practice.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 28F128J3A | 3 Volt Intel StrataFlash Memory(3 V 128M位Strata閃速存儲(chǔ)器) |

| 28F320J3A | 3 Volt Intel StrataFlash Memory(3 V 32M位英特爾StrataFlash存儲(chǔ)器) |

| 28F640J3A | 3 Volt Intel StrataFlash Memory(3 V 64M位英特爾StrataFlash存儲(chǔ)器) |

| 28F128 | 3 Volt Intel StrataFlash Memory |

| 28F1602C3 | 3 Volt Advanced+ Stacked Chip Scale Package Memory(3V閃速存儲(chǔ)器和靜態(tài)存儲(chǔ)器) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 28F020-150 | 制造商: 功能描述: 制造商:undefined 功能描述: |

| 28F020G12 | 制造商: 功能描述: 制造商:undefined 功能描述: |

| 28F020N12 | 制造商: 功能描述: 制造商:undefined 功能描述: |

| 28F020N-15 | 制造商: 功能描述: 制造商:undefined 功能描述: |

| 28F020N-90 | 制造商: 功能描述: 制造商:undefined 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。