- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄298744 > A42MX16-3BG100 (Electronic Theatre Controls, Inc.) 40MX and 42MX FPGA Families PDF資料下載

參數(shù)資料

| 型號(hào): | A42MX16-3BG100 |

| 廠商: | Electronic Theatre Controls, Inc. |

| 英文描述: | 40MX and 42MX FPGA Families |

| 中文描述: | 40MX和42MX FPGA系列 |

| 文件頁(yè)數(shù): | 74/120頁(yè) |

| 文件大小: | 854K |

| 代理商: | A42MX16-3BG100 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)當(dāng)前第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)第94頁(yè)第95頁(yè)第96頁(yè)第97頁(yè)第98頁(yè)第99頁(yè)第100頁(yè)第101頁(yè)第102頁(yè)第103頁(yè)第104頁(yè)第105頁(yè)第106頁(yè)第107頁(yè)第108頁(yè)第109頁(yè)第110頁(yè)第111頁(yè)第112頁(yè)第113頁(yè)第114頁(yè)第115頁(yè)第116頁(yè)第117頁(yè)第118頁(yè)第119頁(yè)第120頁(yè)

57

4958B–AUTO–11/10

Atmel ATA6285/ATA6286 [Preliminary]

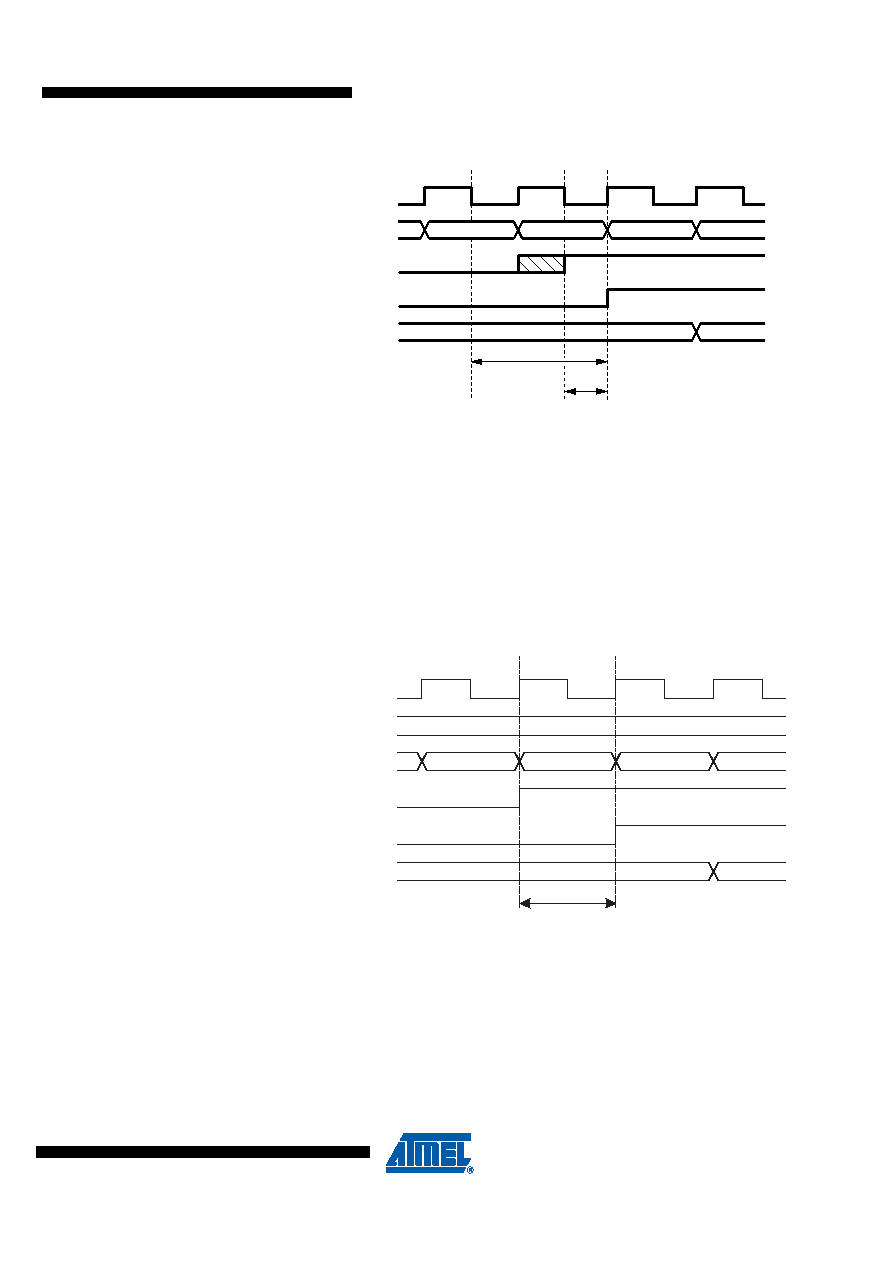

Figure 3-23. Synchronization when Reading an Externally Applied Pin Value

Consider the clock period starting shortly after the first falling edge of the system clock. The latch

is closed when the clock is low, and goes transparent when the clock is high, as indicated by the

shaded region of the “SYNC LATCH” signal. The signal value is latched when the system clock

goes low. It is clocked into the PINxn Register at the succeeding positive clock edge. As indi-

cated by the two arrows tpd,max and tpd,min, a single signal transition on the pin will be delayed

between and 1 system clock period depending upon the time of assertion.

When reading back a software assigned pin value, a nop instruction must be inserted as indi-

cated in Figure 3-24. The out instruction sets the “SYNC LATCH” signal at the positive edge of

the clock. In this case, the delay tpd through the synchronizer is 1 system clock period.

Figure 3-24. Synchronization when Reading a Software Assigned Pin Value

tpd,max

tpd,min

0xFF

0x00

XXX

in r17,PINx

XXX

INSTRUCTIONS

SYNC LATCH

r17

PINxn

SYSTEM CLK

0xFF

0x00

nop

in r17, PINx

SYSTEM CLK

INSTRUCTIONS

SYNC LATCH

PINxn

r17

t

pd

0xFF

out PORTx, r16

r16

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| A42MX16-3PL100 | 40MX and 42MX FPGA Families |

| A42MX16-3PL100A | 40MX and 42MX FPGA Families |

| A42MX16-3PQ100A | 40MX and 42MX FPGA Families |

| A42MX16-3VQ100 | 40MX and 42MX FPGA Families |

| A42MX16-3VQ100A | 40MX and 42MX FPGA Families |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| A42MX16-3BG100A | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:40MX and 42MX FPGA Families |

| A42MX16-3BG100B | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:40MX and 42MX FPGA Families |

| A42MX16-3BG100ES | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:40MX and 42MX FPGA Families |

| A42MX16-3BG100I | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:40MX and 42MX FPGA Families |

| A42MX16-3BG100M | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:40MX and 42MX FPGA Families |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。