- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄16537 > AD9558/PCBZ (Analog Devices Inc)BOARD EVAL FOR AD9558 PDF資料下載

參數(shù)資料

| 型號: | AD9558/PCBZ |

| 廠商: | Analog Devices Inc |

| 文件頁數(shù): | 67/104頁 |

| 文件大小: | 0K |

| 描述: | BOARD EVAL FOR AD9558 |

| 產(chǎn)品變化通告: | AD9558 Minor Metal Mask Change 17/Apr/2012 |

| 設(shè)計資源: | AD9558 Eval Brd BOM AD9558 Schematic |

| 標準包裝: | 1 |

| 系列: | * |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁當前第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁

Data Sheet

AD9558

Rev. B | Page 65 of 104

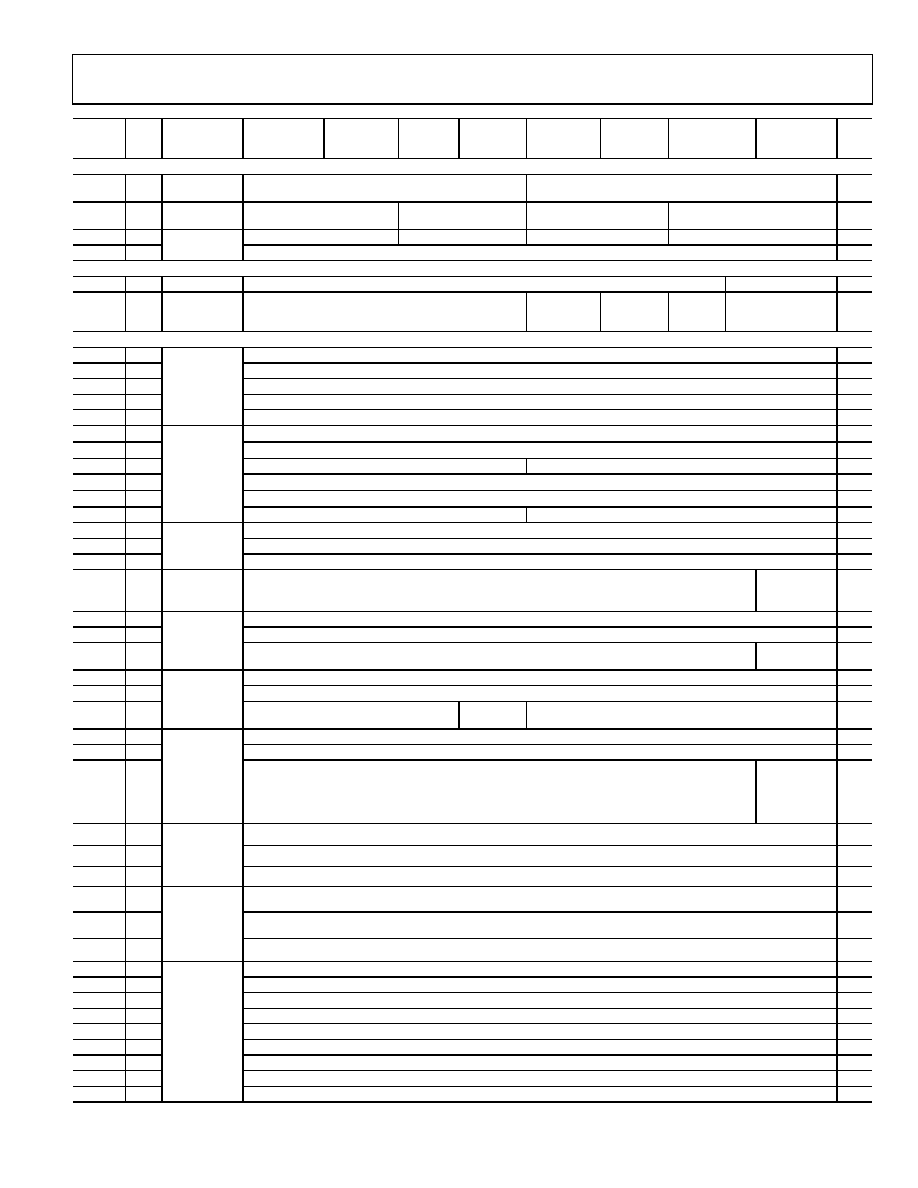

Reg

Addr

(Hex)

Opt

Name

D7

D6

D5

D4

D3

D2

D1

D0

Def

Reference Inputs

0x0600

Reference

power-down

Reserved

Reference power-down[3:0]

00

0x0601

Reference

logic type

REFD logic type[1:0]

REFC logic type[1:0]

REFB logic type[1:0]

REFA logic type[1:0]

00

0x0602

Reference

priority

REFD priority[1:0]

REFC priority[1:0]

REFB priority[1:0]

REFA priority[1:0]

00

0x0603

Reserved

00

Frame Synchronization Mode

0x0640

En frame sync

Reserved

Enable Fsync

00

0x0641

Frame sync

options

Reserved

Validate

Fsync ref

Fsync one

shot

Fsync

arm

method

Arm soft Fsync

00

Profile A (for REFA)

0x0700

L

Reference

period (up to

1.1 ms)

Nominal reference period (fs), Bits[7:0] (default: 51.44 ns =1/(19.44 MHz) for default system clock setting)

C9

0x0701

L

Nominal period (fs), Bits[15:8]

EA

0x0702

L

Nominal period (fs), Bits[23:16]

10

0x0703

L

Nominal period (fs), Bits[31:24]

03

0x0704

L

Nominal period (fs), Bits[39:32]

00

0x0705

L

Frequency

tolerance

Inner tolerance (1 ppm), Bits[7:0] (for reference invalid to valid; 50% down to 1 ppm) (default: 5%)

14

0x0706

L

Inner tolerance (1 ppm), Bits[15:8] (for reference invalid to valid; 50% down to 1 ppm)

00

0x0707

L

Reserved

Inner tolerance, Bits[19:16]

00

0x0708

L

Outer tolerance (1 ppm), Bits[7:0] (for reference valid to invalid; 50% down to 1 ppm) (default: 10%)

0A

0x0709

L

Outer tolerance (1 ppm), Bits[15:8] (for reference valid to invalid; 50% down to 1 ppm)

00

0x070A

L

Reserved

Outer tolerance, Bits[19:16]

00

0x070B

L

Validation

Validation timer (ms), Bits[7:0] (up to 65.5 seconds)

0A

0x070C

L

Validation timer (ms), Bits[15:8] (up to 65.5 seconds)

00

0x070D

L

Reserved

00

0x070E

L

Select base

loop filter

Reserved

Sel high PM

base loop

filter

00

0x070F

L

DPLL loop BW

Digital PLL loop BW scaling factor[7:0] (default: 0x01F4 = 50 Hz)

F4

0x0710

L

Digital PLL loop BW scaling factor[15:8]

01

0x0711

L

Reserved

BW scaling

factor[16]

00

0x0712

L

DPLL

R divider

(20 bits)

R divider[7:0]

C5

0x0713

L

R divider[15:8]

00

0x0714

L

Reserved

Enable REFA

divide-by-2

R divider[19:16]

00

0x0715

DPLL

N divider

(17 bits)

Digital PLL feedback divider—Integer Part N1[7:0]

6B

0x0716

Digital PLL feedback divider—Integer Part N1[15:8]

07

0x0717

Reserved

Digital PLL

feedback

divider—

Integer Part

N1[16]

00

0x0718

DPLL

fractional

feedback

divider

(24 bits)

Digital PLL fractional feedback divider—FRAC1[7:0]

04

0x0719

Digital PLL fractional feedback divider—FRAC1[15:8]

00

0x071A

Digital PLL fractional feedback divider—FRAC1[23:16]

00

0x071B

DPLL

fractional

feedback

divider

modulus

(24 bits)

Digital PLL feedback divider modulus—MOD1[7:0]

05

0x071C

Digital PLL feedback divider modulus—MOD1[15:8]

00

0x071D

Digital PLL feedback divider modulus—MOD1[23:16]

00

0x071E

L

Lock detectors

Phase lock threshold (ps), Bits[7:0]

BC

0x071F

L

Phase lock threshold (ps), Bits[15:8]

02

0x0720

L

Phase lock fill rate[7:0]

0A

0x0721

L

Phase lock drain rate[7:0]

0A

0x0722

L

Frequency lock threshold[7:0]

BC

0x0723

L

Frequency lock threshold[15:8]

02

0x0724

L

Frequency lock threshold[23:16]

00

0x0725

L

Frequency lock fill rate[7:0]

0A

0x0726

L

Frequency lock drain rate[7:0]

0A

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| GBM22DSAH | CONN EDGECARD 44POS R/A .156 SLD |

| DK-2632-03 | CABLE FIBER OPTIC DUAL LC-SC 3M |

| GEM30DTAS | CONN EDGECARD 60POS R/A .156 SLD |

| GMM12DRXI | CONN EDGECARD 24POS DIP .156 SLD |

| P1330R-105K | INDUCTOR POWER 1000.0UH SMD |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| AD9559 | 制造商:AD 制造商全稱:Analog Devices 功能描述:Dual PLL, Quad Input, Multiservice Line Card Adaptive Clock Translator |

| AD9559/PCBZ | 功能描述:時鐘和定時器開發(fā)工具 Multi-protocol line card dual clock RoHS:否 制造商:Texas Instruments 產(chǎn)品:Evaluation Modules 類型:Clock Conditioners 工具用于評估:LMK04100B 頻率:122.8 MHz 工作電源電壓:3.3 V |

| AD9559BCPZ | 功能描述:時鐘發(fā)生器及支持產(chǎn)品 Multi-protocol line card dual clock RoHS:否 制造商:Silicon Labs 類型:Clock Generators 最大輸入頻率:14.318 MHz 最大輸出頻率:166 MHz 輸出端數(shù)量:16 占空比 - 最大:55 % 工作電源電壓:3.3 V 工作電源電流:1 mA 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:QFN-56 |

| AD9559BCPZ-REEL7 | 功能描述:時鐘發(fā)生器及支持產(chǎn)品 Multi-protocol line card dual clock RoHS:否 制造商:Silicon Labs 類型:Clock Generators 最大輸入頻率:14.318 MHz 最大輸出頻率:166 MHz 輸出端數(shù)量:16 占空比 - 最大:55 % 工作電源電壓:3.3 V 工作電源電流:1 mA 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:QFN-56 |

| AD9559PCBZ | 制造商:AD 制造商全稱:Analog Devices 功能描述:Dual PLL, Quad Input, Multiservice Line Card Adaptive Clock Translator |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。