- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄376727 > DK1241A (Electronic Theatre Controls, Inc.) Advanced Microstepping Motion Control Chipset PDF資料下載

參數(shù)資料

| 型號: | DK1241A |

| 廠商: | Electronic Theatre Controls, Inc. |

| 英文描述: | Advanced Microstepping Motion Control Chipset |

| 中文描述: | 高級微步運(yùn)動控制芯片組 |

| 文件頁數(shù): | 14/60頁 |

| 文件大小: | 422K |

| 代理商: | DK1241A |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁當(dāng)前第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁

14

IC

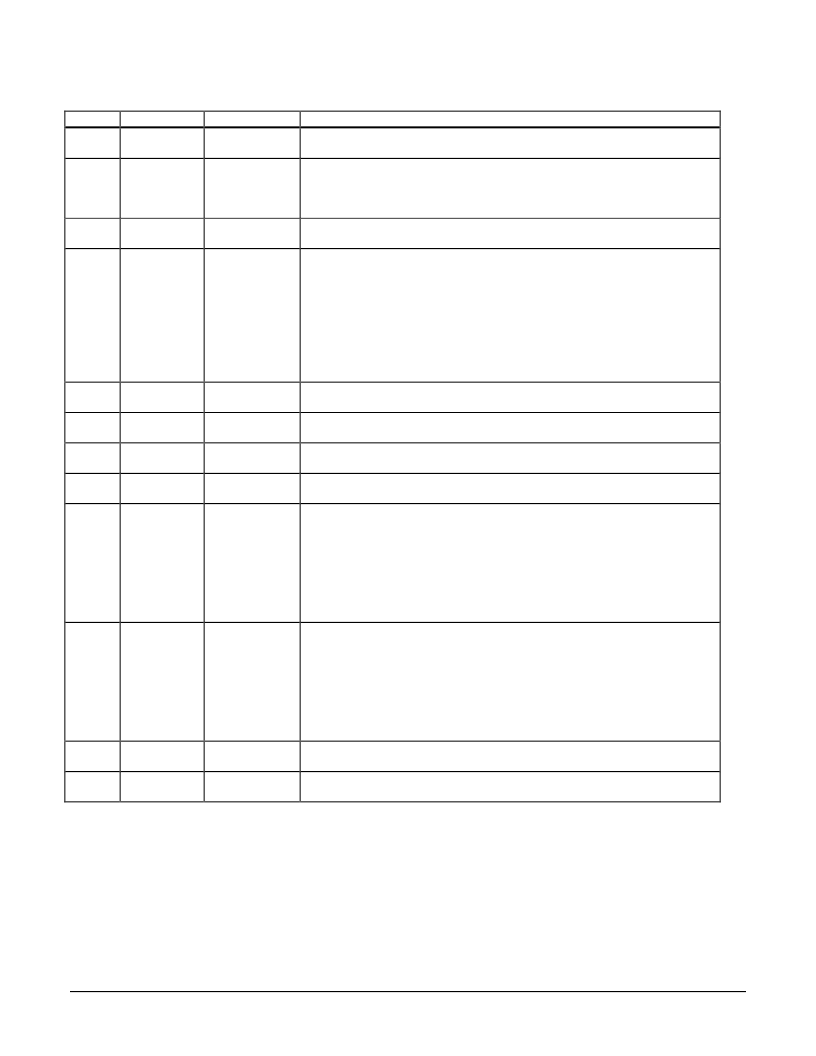

I/O

Pin Name

~CPWrite

Pin #

2

Description/Functionality

I/O chip to CP chip communication write (input). This signal is connected to the ~I/OWrite pin

(CP chip) and provides a write strobe to facilitate CP to I/O chip communication.

I/O chip to CP chip communication control (mxed). These 4 signals are connected to the

corresponding I/OCntrl0-3 pins (CP chip), and provide control signals to facilitate CP to I/O

chip communication.

I/O

CPCntrl0

CPCntrl1

CPCntrl2

CPCntrl3

HostCmd

20

36

22

63

41

I/O

Host Port Command (input). This signal is asserted high to write a host command to the chip

set. It is asserted low to read or write a host data word to the chipset

Host Port Ready/Busy (output). This signal is used to synchronize communication between

the DSP and the host. HostRdy will go low (indicating host port busy) at the end of a host

command write or after the second byte of a data write or read. HostRdy will go high

(indicating host port ready) when the command or data word has been processed and the

chip set is ready for more I/O operations. All host port communications must be made with

HostRdy high (indicating ready).

I/O

HostRdy

37

Typical busy to ready cycle is 67.5 uSec, although it can be longer when host port traffic is

high.

Host Port Read data (input). Used to indicate that a data word is being read fromthe chip set

(low asserts read).

Host Port Write data (input). Used to indicate that a data word or command is being written to

the chip set (low asserts write).

Host Port Select (input). Used to select the host port for reading or writing operations (low

assertion selects port). ~HostSlct must remain inactive (high) when the host port is not in use.

Host Interrupt (output). A low assertion on this pin indicates that a host interrupt condition

exists that may require special host action.

Host Port Data 0-7 (bi-directional, tri-stated). These signals formthe 8 bit host data port used

during communication to/fromthe chip set. This port is controlled by ~HostSlct, ~HostWrite,

~HostRead and HostCmd.

I/O

~HostRead

51

I/O

~HostWrite

47

I/O

~HostSlct

48

I/O

~HostIntrpt

44

I/O

HostData0

HostData1

HostData2

HostData3

HostData4

HostData5

HostData6

HostData7

CPData4

CPData5

CPData6

CPData7

CPData8

CPData9

CPData10

CPData11

Vcc

50

61

53

65

67

62

64

60

18

5

6

7

8

17

3

1

4, 21, 25, 38, 55

I/O

I/O chip to CP chip data port (bi-directional). These 8 bits are connected to the corresponding

Data4-11 pins on the CP chip, and facilitate communication to/fromthe I/O and CP chips..

I/O

I/O chip supply voltage pin. All of these pins must be connected to the supply voltage. Supply

voltage = 4.75 to 5.25 V

I/O chip ground pin. All of these pins must be connected to the power supply return.

I/O

GND

14, 15, 32, 49, 54,

66

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| DK2100 | Navigator Motion Processor |

| DK3300 | Turbo uPSD DK3300 User Manual(Turbo系列 uPSD DK3300 用戶手冊) |

| DK60 | DIODY PROSTOWNICZE |

| DK61 | DIODY PROSTOWNICZE |

| DK62 | DIODY PROSTOWNICZE |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| DK125950 | 制造商:TE Connectivity 功能描述: |

| DK-125M-1 | 制造商:Luminus Devices 功能描述:EVAL BOARD & HEAT SINK FOR PT85/CBT85. MAX16818, 25A, 1 CH - Bulk |

| DK12GY | 功能描述:電氣外殼 RoHS:否 制造商:Bud Industries 產(chǎn)品:Wall Mount Enclosures 類型:Single Door NEMA 額定值:3R 外部深度:254 mm 外部高度:305 mm 外部寬度:305 mm 面板寬度:261 mm 面板高度:261 mm 材料:Steel 顏色:Gray 通風(fēng):Not Available |

| DK12LG | 功能描述:電氣外殼 RoHS:否 制造商:Bud Industries 產(chǎn)品:Wall Mount Enclosures 類型:Single Door NEMA 額定值:3R 外部深度:254 mm 外部高度:305 mm 外部寬度:305 mm 面板寬度:261 mm 面板高度:261 mm 材料:Steel 顏色:Gray 通風(fēng):Not Available |

| DK12S16 | 功能描述:電氣外殼 RoHS:否 制造商:Bud Industries 產(chǎn)品:Wall Mount Enclosures 類型:Single Door NEMA 額定值:3R 外部深度:254 mm 外部高度:305 mm 外部寬度:305 mm 面板寬度:261 mm 面板高度:261 mm 材料:Steel 顏色:Gray 通風(fēng):Not Available |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。