- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄371054 > MC68SC302 (Motorola, Inc.) 32-Bit Microprocessor(32位微處理器) PDF資料下載

參數(shù)資料

| 型號: | MC68SC302 |

| 廠商: | Motorola, Inc. |

| 英文描述: | 32-Bit Microprocessor(32位微處理器) |

| 中文描述: | 32位微處理器(32位微處理器) |

| 文件頁數(shù): | 73/218頁 |

| 文件大?。?/td> | 521K |

| 代理商: | MC68SC302 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁當前第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁第128頁第129頁第130頁第131頁第132頁第133頁第134頁第135頁第136頁第137頁第138頁第139頁第140頁第141頁第142頁第143頁第144頁第145頁第146頁第147頁第148頁第149頁第150頁第151頁第152頁第153頁第154頁第155頁第156頁第157頁第158頁第159頁第160頁第161頁第162頁第163頁第164頁第165頁第166頁第167頁第168頁第169頁第170頁第171頁第172頁第173頁第174頁第175頁第176頁第177頁第178頁第179頁第180頁第181頁第182頁第183頁第184頁第185頁第186頁第187頁第188頁第189頁第190頁第191頁第192頁第193頁第194頁第195頁第196頁第197頁第198頁第199頁第200頁第201頁第202頁第203頁第204頁第205頁第206頁第207頁第208頁第209頁第210頁第211頁第212頁第213頁第214頁第215頁第216頁第217頁第218頁

Communications Processor (CP)

MOTOROLA

MC68SC302 USER’S MANUAL

4-27

be disabled if only a change to a parameter RAM value is made. See Table 4-3

for a

description of which parameter RAM values may be modified.

To save power, the SCCs may simply be disabled. Clearing the enable transmitter (ENT) bit

in the SCC mode register causes the SCC transmitter to consume the least possible power;

clearing the ENR bit causes a similar action for the SCC receiver.

4.5.10 HDLC Controller

Layer 2 of the seven-layer OSI model is the data link layer. One of the most common layer

2 protocols is HDLC. Many other common layer 2 protocols are heavily based on HDLC,

particularly its framing structure, namely: SDLC, SS#7, LAPB, and LAPD. The framing

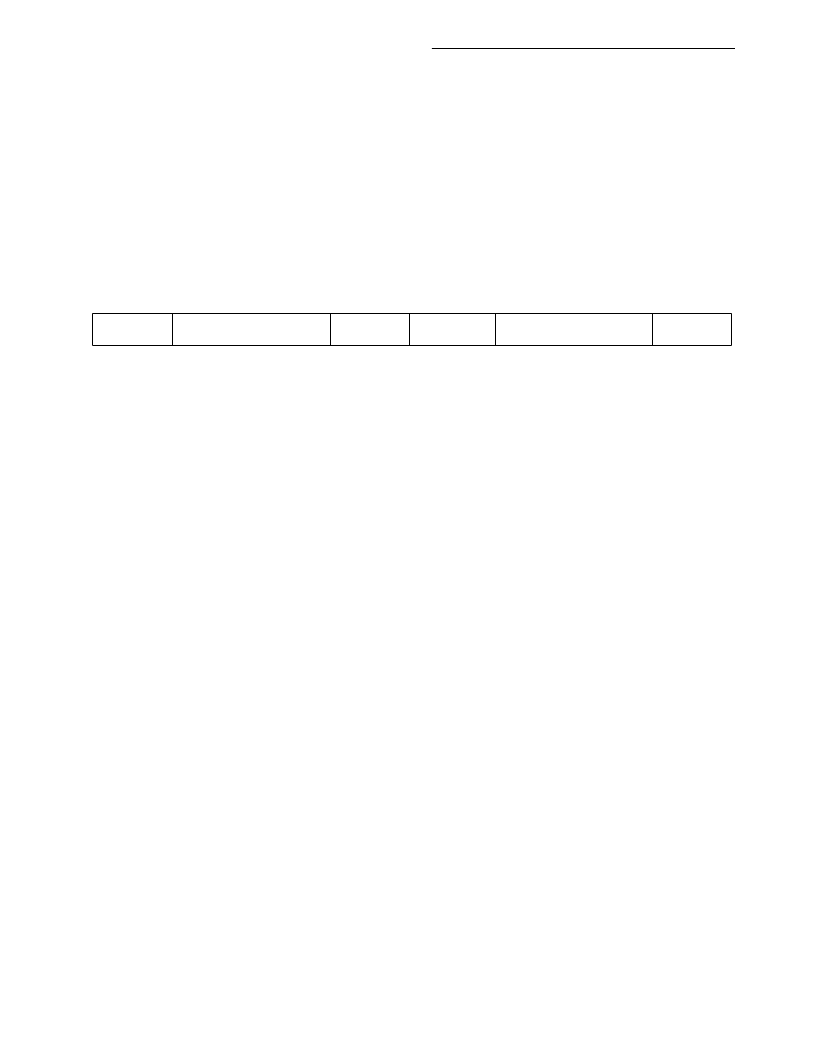

structure of HDLC is shown in Figure 4-9.

Figure 4-9. Typical HDLC Frame

HDLC uses a zero insertion/deletion process (commonly known as bit-stuffing) to ensure

that the bit pattern of the delimiter flag does not occur in the fields between flags. The HDLC

frame is synchronous and therefore relies on the physical layer to provide a method of

clocking and synchronizing the transmitter and receiver.

Since the layer 2 frame can be transmitted over a point-to-point link, a broadcast network,

or packet and circuit-switched systems, an address field is needed to carry the frame's

destination address. The length of this field is commonly 0, 8, or 16 bits, depending on the

data link layer protocol. For instance, SDLC and LAPB use an 8-bit address. SS#7 has no

address field at all because it is always used in point-to-point signaling links. LAPD further

divides its 16-bit address into different fields to specify various access points within one

piece of equipment. It also defines a broadcast address. Some HDLC-type protocols also

allow for extended addressing beyond 16-bits.

The 8- or 16-bit control field provides a flow control number and defines the frame type

(control or data). The exact use and structure of this field depends upon the protocol using

the frame.

Data is transmitted in the data field, which can vary in length depending upon the protocol

using the frame. Layer 3 frames are carried in the data field.

Error control is implemented by appending a cyclic redundancy check (CRC) to the frame,

which is 16-bits long in most protocols, but may be 32-bits long in some.

When the MODE bit of an SCC mode register (SCM) selects HDLC mode, then that SCC

functions as an HDLC controller. The HDLC controller handles the basic functions of the

HDLC/SDLC protocol on either the D channel, a B channel, or from a multiplexed serial

interface (IDL or GCI (IOM-2)). When the HDLC controller is used to support the B or D

OPENING

FLAG

8 BITS

ADDRESS

CONTROL

INFORMATION

(OPTIONAL)

8N BITS

CRC

CLOSING

FLAG

8 BITS

16 BITS

8 BITS

16 BITS

相關PDF資料 |

PDF描述 |

|---|---|

| MC68SEC000D | Dual Audio Operational Amplifier 8-PDIP -40 to 85 |

| MC68SEC000FU20 | Addendum to M68000 User Manual |

| MC68SEC000 | Addendum to M68000 User Manual |

| MC68SEC000CFU10 | M68000 USERS MANUAL ADDENDUM |

| MC68HC000 | 1.25V 100ppm/Degrees C, 50uA in SOT23-3 Series (Bandgap) Voltage Reference 3-SOT-23 -40 to 125 |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| MC68SEC000AA10 | 功能描述:微處理器 - MPU 8/16/32 BIT MPU STATIC RoHS:否 制造商:Atmel 處理器系列:SAMA5D31 核心:ARM Cortex A5 數(shù)據(jù)總線寬度:32 bit 最大時鐘頻率:536 MHz 程序存儲器大小:32 KB 數(shù)據(jù) RAM 大小:128 KB 接口類型:CAN, Ethernet, LIN, SPI,TWI, UART, USB 工作電源電壓:1.8 V to 3.3 V 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:FBGA-324 |

| MC68SEC000AA10R2 | 功能描述:IC MPU 32BIT 10MHZ 64-QFP RoHS:是 類別:集成電路 (IC) >> 嵌入式 - 微處理器 系列:M680x0 標準包裝:2 系列:MPC8xx 處理器類型:32-位 MPC8xx PowerQUICC 特點:- 速度:133MHz 電壓:3.3V 安裝類型:表面貼裝 封裝/外殼:357-BBGA 供應商設備封裝:357-PBGA(25x25) 包裝:托盤 |

| MC68SEC000AA16 | 功能描述:微處理器 - MPU 8/16/32 BIT MPU STATIC RoHS:否 制造商:Atmel 處理器系列:SAMA5D31 核心:ARM Cortex A5 數(shù)據(jù)總線寬度:32 bit 最大時鐘頻率:536 MHz 程序存儲器大小:32 KB 數(shù)據(jù) RAM 大小:128 KB 接口類型:CAN, Ethernet, LIN, SPI,TWI, UART, USB 工作電源電壓:1.8 V to 3.3 V 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:FBGA-324 |

| MC68SEC000AA16 | 制造商:Freescale Semiconductor 功能描述:Microprocessor |

| MC68SEC000AA16R2 | 功能描述:微處理器 - MPU 8/16/32 BIT MPU STATIC RoHS:否 制造商:Atmel 處理器系列:SAMA5D31 核心:ARM Cortex A5 數(shù)據(jù)總線寬度:32 bit 最大時鐘頻率:536 MHz 程序存儲器大小:32 KB 數(shù)據(jù) RAM 大小:128 KB 接口類型:CAN, Ethernet, LIN, SPI,TWI, UART, USB 工作電源電壓:1.8 V to 3.3 V 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:FBGA-324 |

發(fā)布緊急采購,3分鐘左右您將得到回復。